GE VMIVME-5565 Ultra High Speed Fiber Reflective Memory (with Interrupt Function)

Switch/jumper configuration and position

Node ID Switch (S6): An 8-bit switch that sets the node ID within the range of 0 to 255. Each node ID must be unique, and the switch position "ON" corresponds to 0, while "OFF" corresponds to 1.

Jumper E5 (redundant mode configuration): Used to configure redundant or non redundant transmission modes and select abnormal master nodes, with different pin hopping states corresponding to different functions.

Register and memory configuration switch: VMIVME-5565 occupies two independent address spaces on VMEbus. The control and status register spaces can be set as extended address space (A32) or standard address space (A24), and the SDRAM memory space can be set as extended address space (A32). When configuring, address overlap should be avoided. The switch "ON" corresponds to address bit 0, and "OFF" corresponds to address bit 1.

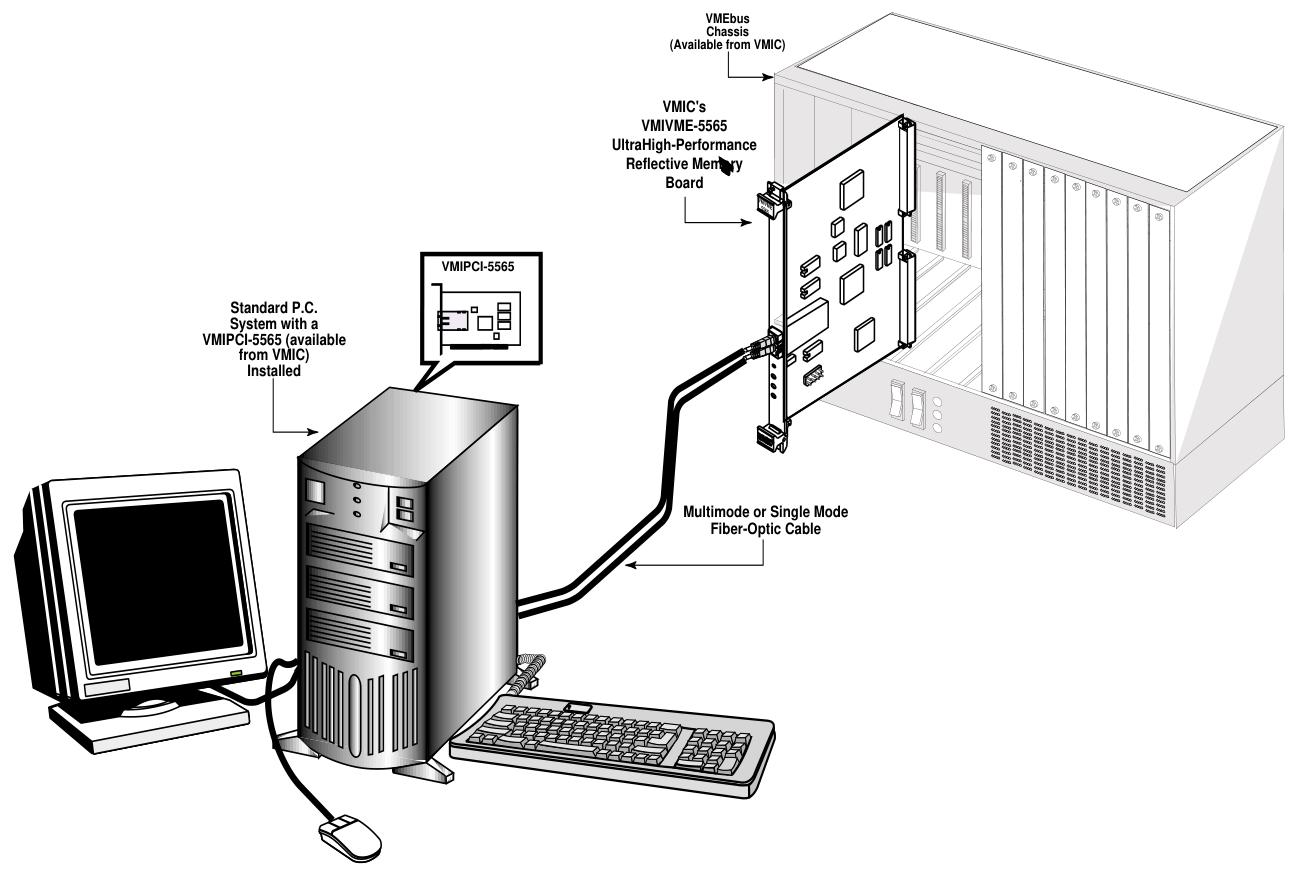

Physical installation: Power off installation, ensure correct switch settings, fix after installation on the chassis, and connect fiber optic cables according to the ring topology.

Front panel description: Optical transceiver, "RX" for receiver, "TX" for transmitter, using "LC" type fiber optic cable, with three LED indicator lights as described earlier. When operating, pay attention to dust prevention and avoid looking directly at the transmitter.

Cable configuration: There are multi-mode or single mode fiber optic interfaces, and cables and connectors have specific specifications.

Connectivity: Nodes are connected in a circular manner.

Programming

RFM Control and Status Register: Located at a specific offset address, it includes local control and status registers, local interrupt status registers, local interrupt enable registers, etc. Each register has different functions and bit definitions.

RFM network registers: including Network Target Data Register (NTD), Network Target Node Register (NTN), Network Interrupt Command Register (NIC), as well as various interrupt sender IDs and data FIFOs, used for generating and receiving network interrupts.

Example of network interrupt handling: including the steps for setting interrupt programs and serving network interrupts.

Universe II registers: divided into Universe II control and status registers and Universe II DMA registers, each with different offset addresses, functions, and bit definitions, which can be used to control and monitor interrupts and DMA transfers.

DMA source and destination addresses: determined by specific registers, transfer direction determined by L2V bits, alignment requirements for addresses, adjustable transfer size and data width, DMA command packet pointer pointing to command packet, DMA startup, VMEbus ownership, completion, and termination all have corresponding operations and mechanisms.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba