GE VMIVME-2528 128 bit TTL digital I/O TURBOModule ™

Document information: Document number 500-002528-000N, revised on September 30, 1994

Company Information: Produced by VME Microsystems International Corporation, with a company address of 12090 South Memorial Parkway, Huntsville, AL 35803-3308, Contact phone numbers (205) 880-0444, 1-800-322-3616

Trademark information: BITMODULE ™、 MEGAMODULE ™、 TURBOMODULE ™ The VMIC logo is a registered trademark of the company

GE VMIVME-2528 128 bit TTL digital I/O TURBOModule ™

Basic Information

Product Name: VMIVME-2528 128 bit TTL Digital I/O TURBOModule ™

Document information: Document number 500-002528-000N, revised on September 30, 1994

Company Information: Produced by VME Microsystems International Corporation, with a company address of 12090 South Memorial Parkway, Huntsville, AL 35803-3308, Contact phone numbers (205) 880-0444, 1-800-322-3616

Trademark information: BITMODULE ™、 MEGAMODULE ™、 TURBOMODULE ™ The VMIC logo is a registered trademark of the company

Security Summary

Grounding requirements: To reduce the risk of electric shock, the chassis and system cabinets must be connected to electrical grounding, using a three core AC power cord and correctly grounded

Environmental restrictions: Equipment must not be operated in explosive atmospheres

Circuit safety: Operators must not remove the product casing, component replacement and internal adjustment must be carried out by qualified maintenance personnel, and components must not be replaced before power failure. Even if there is a power failure, dangerous voltage may still exist in some situations, and discharge is required before operation

Maintenance precautions: Internal repairs or adjustments must not be carried out independently, and personnel with first aid and resuscitation capabilities must be present; Do not replace components or modify the system, repairs should be returned to the company for further processing

Safety symbols: including reference manual symbols, dangerous voltage symbols, protective conductor terminal symbols, and other safety symbols and their meanings

Warning and Caution: "Warning" indicates a danger that may result in personal injury or death; CAUTION "indicates the potential danger of system damage; NOTE "indicates important information

Introduction

Product Features

128 bit TTL input/output

16 8-bit I/O port jumpers, allowing for selection of input or output operations on 8-bit boundaries

24mA current injection capability

Supports 8-bit or 16 bit data transmission

Function description: High density TTL I/O board, supports up to 128 bit TTL input or output through user installed port direction control jumpers. Each jumper sets an 8-bit port as an input or output port, and each output has a current absorption capacity of up to 24mA. It is designed with a high-quality ground plane to enhance noise resistance. When the system is reset, all I/O ports are initialized to inactive state, and all ports are activated by writing to I/O register 7

Reference materials: including "The VMEbus Specification" and various application and configuration guides provided by VMIC, such as "Digital Input Board Application Guide"

Working principle

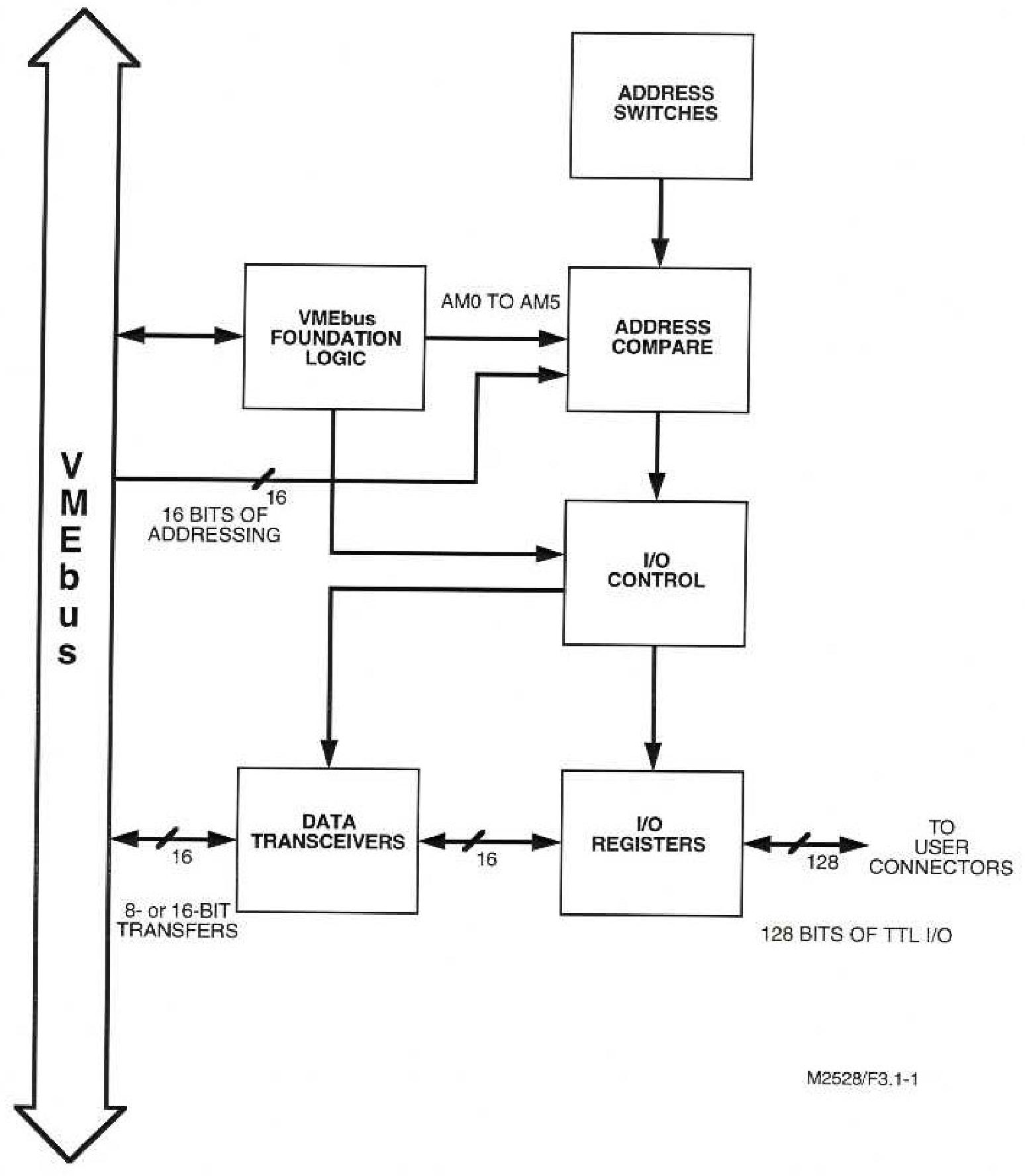

Block diagram: The functional block diagram is divided into six sub parts: VMEbus basic logic, data transceiver, address comparison logic, read/write register control logic, registers 0-3, and registers 4-7. There are also multiple subsystem block diagrams

Board addressing: supports data transmission of monitoring or non privileged short I/O memory space, selects I/O access type through jumper, factory configured to respond to short monitoring I/O access, and has two board selection DIP switches for setting the board's base address

VMEbus basic logic: including typical VMEbus drivers, receivers, and control logic

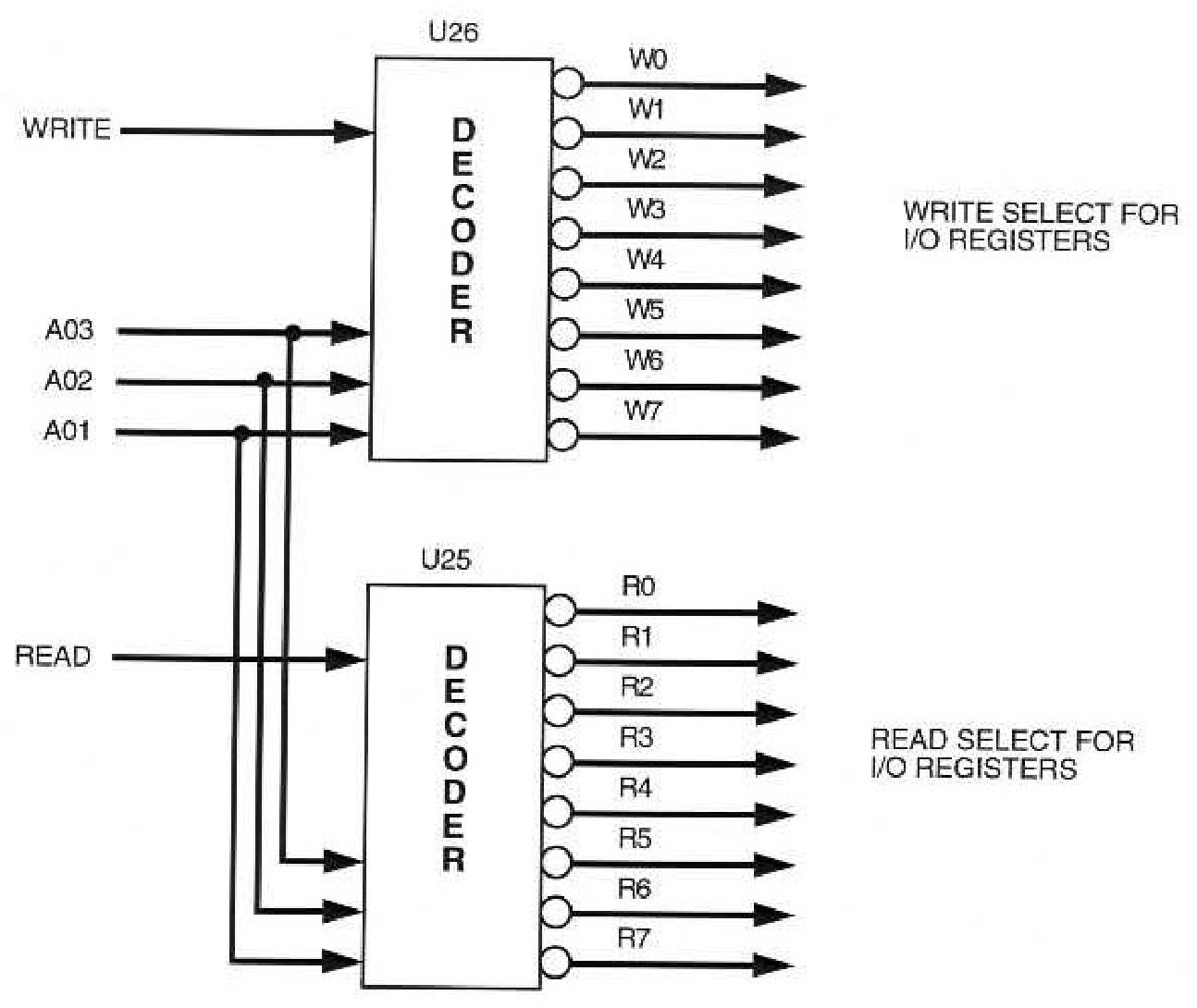

Register read/write control logic: Address bits A01, A02, A03 and read/write control lines are decoded into eight write control lines and eight read control lines, routed to the enable pins of each bidirectional latch, which can be selected for read or write operations through jumper wires

Data transmission description: The corresponding I/O data register is selected for data transmission through address bits A3, A2, and A1 combined with a data gating signal. The board selection signal generates an active signal for data transmission with DSO and DS1 logic gates. The board selection also activates a delay signal to generate a delayed version, which is used to provide setup time for the data transceiver during the write cycle before locking the data into the I/O register. The DTACK signal indicates that the data has been latched (write cycle) or is valid (read cycle)

I/O port enable description: The system reset signal (powered on or initiated by the VMEbus master device) disables all I/O ports/registers, and enables all I/O ports by writing to the I/O register R7L, regardless of whether they are configured as input or output ports

Programming

I/O register mapping: 12 bit addresses (A15 to A04) are used for board selection decoding, and the address switch is set to match these bits to generate data transfer board selection signals. The 128 bit I/O is divided into eight 16 bit registers for word transfer, and address bits A03, A02, and A01 are used to decode one of the eight registers, with a detailed I/O register mapping table

I/O port direction: Programming should be consistent with the I/O configuration selected by the jumper in the I/O port direction. The output port can only write data, and the input port can only read data. Please refer to Section 5 for jumper configuration details

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba