TEKTRONIX VX4240 VXIbus protocol waveform digitizer/analyzer module

Communication failure: 1. Logical address setting conflict; 2. VXIbus bus failure; 3. Command format error: 1. Reset the logical address (to avoid conflicts with other modules); 2. Check the bus connection of the host rack; 3. Ensure that the command string conforms to syntax (ASCII characters, correct delimiter)

Extension options and compatibility

1. Extension options

Option 01:512K word sampling memory expansion.

Option 02: 1M word sampling memory expansion.

Option 2A (waveform output): Supports digital signal playback, programmable delay (200 ns to 420 s), output amplitude ± 1Vpp or ± 10Vpp (50 Ω load), and needs to be used in conjunction with a waveform output card.

2. Compatibility

Host rack compatibility: Supports all C/D size host racks that comply with VXIbus specifications, and Slot 0 requires a resource manager (such as VX4521).

Interface compatibility: Supports VXIbus serial protocol, compatible with IEEE-488 (GPIB) interface (requires conversion through Slot 0 module), configurable interrupt level (1-7 levels).

Software compatibility: Provides BASIC programming language sample programs and supports mainstream measurement and control software (must follow VXIbus instrument protocol commands).

Summary of Key Appendix Information

1. Appendix Core Content

Appendix A (VXIbus Operations): Detailed explanation of module VXIbus register definition, transfer mode (normal transfer/fast handshake), and interrupt handling process.

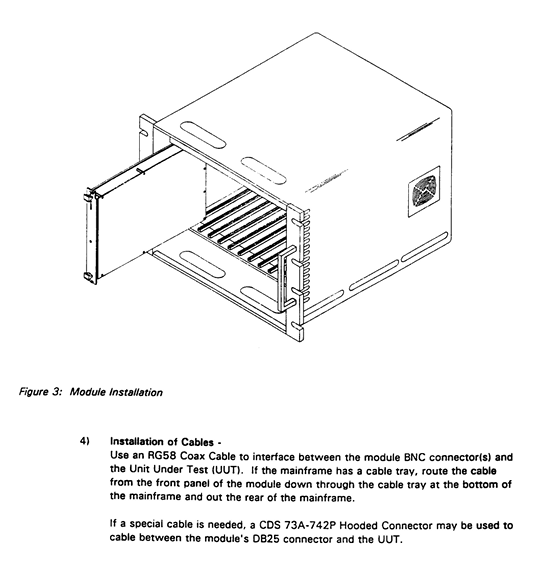

Appendix B (I/O Connections): Provide pin definitions, signal grounding requirements, and external trigger/clock/ARM signal interface specifications for BNC and DB25 connectors.

Appendix E (Fourier Transform): Explain the FFT principle, spectral leakage suppression (window function effect), and sampling frequency selection principle (Nyquist theorem).

Appendix H (Performance Verification): Provide the verification process and equipment requirements for key indicators such as DC accuracy, AC accuracy, and Common Mode Rejection Ratio (CMRR).

Appendix I (Calibration Process): Detailed description of the operation steps and adjustment of potentiometer positions for DC gain/offset calibration, AC gain calibration, and common mode rejection calibration.

2. Important Notice

Binary transmission: When using the National Instruments GPIB-VXI/C Slot 0 module, a dedicated code instrument (CI) needs to be loaded to avoid data buffer residue.

IEEE-488 address configuration: If the GPIB address is not assigned after the system is powered on, the Slot 0 resource manager delay (set to 5 seconds) needs to be adjusted to ensure that the module completes self-test.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba