XYCOM XVME-100 memory module

XYCOM XVME-100 memory module

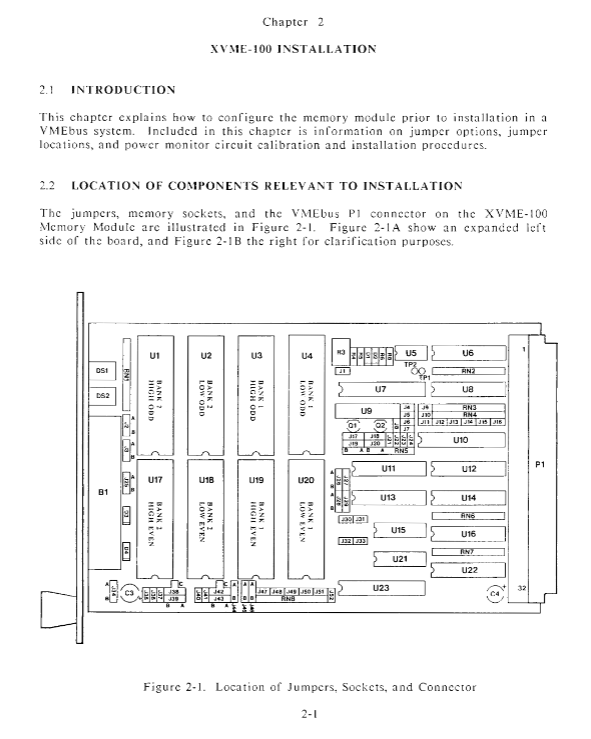

Core positioning and product architecture

1. Product positioning and core values

XYCOM XVME-100 is a 3U single high memory expansion module designed for industrial control systems with VMEbus architecture. Its core positioning is "a highly compatible, configurable, and reliable multi type storage expansion solution". Its core values revolve around the stringent demands of industrial scenarios:

Compatibility: Fully compliant with the VMEbus C1 standard, it can seamlessly integrate into various VMEbus systems and adapt to industrial and military embedded devices;

Flexibility: Supports four storage types: RAM, EPROM, mask ROM, and EEPROM, with independent configuration of dual storage groups, compatible with various capacity chips ranging from 8K × 8 to 128K × 8;

Reliability: Built in battery backup (typical lifespan of 6 years) and undervoltage protection circuit ensure that data is not lost in case of power failure;

Usability: Visual configuration of address, speed, backup power, and other parameters is achieved through jumper cables, supporting hot swappable installation and on-site maintenance.

2. System integration architecture

XVME-100, as the "storage expansion unit" of the VMEbus system, adopts a "modular+bus compatible" architecture. The core consists of four layers: storage core layer, configuration control layer, bus interface layer, and protection mechanism layer

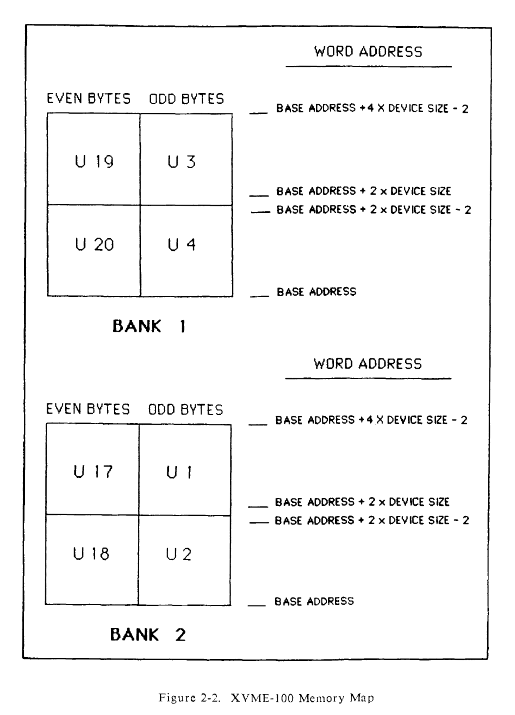

Storage core layer: dual storage group (Bank1/Bank2) design, each group containing 4 32 pin JEDEC slots, supporting mixed storage chip of different types/specifications;

Configuration control layer: Address allocation, chip speed matching, backup power selection and other functions are implemented through 52 jumpers, without the need for additional software configuration;

Bus interface layer: P1 connector (3 rows of pins) compatible with VMEbus address, data, and control signals, supporting A24 address space and DTB slave device roles;

Protection mechanism layer: integrates undervoltage protection (triggered by 4.75V), data write protection, SYSRESET * driver and other functions, combined with backup power supply to form multiple data security guarantees.

Detailed explanation of key specification parameters

1. Core performance parameters

(1) Storage and Configuration Parameter Table

Specific specifications and design value of the project

Maximum storage capacity RAM/EPROM/mask ROM: 1MB;

EEPROM: 256KB covers all scenario storage requirements from small and medium-sized control programs to large data caches

Design 2 storage groups (Bank1/Bank2), each consisting of 4 32 pin JEDEC slots that support mixing of different types/speeds/capacities of chips to enhance configuration flexibility

Compatible chip specifications and capacities: 8K × 8, 16K × 8, 32K × 8, 64K × 8, 128K × 8;

Speed: 100ns, 150ns, 200ns, 250ns Compatible with mainstream industrial grade storage chips, chip speed can be selected according to real-time requirements

Storage types support RAM, EPROM, mask ROM, EEPROM (with support for fast write/polling technology), compatible with program storage (EPROM/ROM), data cache (RAM), power down save (EEPROM), and other different scenarios

The base address for address space configuration can be set through jumper wires. The storage group occupies space equal to the chip capacity multiplied by 4, and needs to be aligned to 4 times the capacity boundary to avoid address conflicts and adapt to complex systems where multiple modules work together

(2) Power and reliability parameter table

Specific specifications and design value of the project

Working power supply+5V DC, typical current 900mA, maximum 1A compatible with industrial standards+5V power supply, low-power design suitable for embedded systems

Backup power board battery (1.4Ah, typical lifespan of 6 years) or VMEbus+5V STDBY signal dual backup solution, suitable for independent devices without continuous backup power and integrated scenarios with system backup power

Under voltage protection threshold+5V ± 5% (triggered by 4.75V) to prevent voltage fluctuations from causing data writing errors or chip damage

Battery life calculation formula: Battery life (hours)=1400000/[(n × IsB)+10], where n is the number of RAM chips and IsB is the data holding current (μ A) of a single chip. The backup time can be accurately estimated based on the characteristics of the selected RAM chip, and maintenance cycles can be planned in advance

2. Physical and environmental parameters

(1) Physical specification details

Specific specifications of the project are adapted to different scenarios

The external dimensions are 3U Form Factor (single height), which conforms to the VMEbus standard size and adapts to the standard VMEbus rack. A single module occupies 1 3U slot and supports dense deployment

Connector type P1 connector (3 rows of pins, total 96 pins) compatible with VMEbus backplane signal definition, ensuring stable bus communication

Weight not clearly indicated, industrial grade modular design, lighter than 500g for rack installation and maintenance, reducing rack load pressure

Optional accessory XVME-945 6U front-end panel kit is suitable for 6U rack installation requirements, improving module fixation reliability

(2) Environmental adaptability parameters

Specific specifications of the project, industrial scenario value

Working temperature range: 0 ° C~65 ° C (32 ° F~149 ° F), suitable for wide temperature environments such as industrial workshops and outdoor equipment cabins

Storage temperature -40 ° C~85 ° C (-40 ° F~158 ° F) to meet extreme temperature environments during storage and transportation

Humidity range of 5% to 95% RH, non condensing (requiring anti-static protection for extremely low humidity), suitable for humid environments such as high humidity workshops and coastal areas, while also indicating requirements for electrostatic protection

Vibration (working) 5~2000Hz, peak acceleration 10g, peak to peak displacement 0.025mm (maximum) to resist vibration interference during industrial equipment operation, ensuring stable module connection

Impact (working) with a peak acceleration of 30g and a duration of 11ms to withstand impacts during transportation or on-site operations, enhancing the equipment's ability to withstand harsh environments

Altitude work: 0~3048m (10000ft); Storage: 0~15240m (50000ft) suitable for special geographical environments such as high-altitude areas

Core functions and design highlights

1. Core functions of storage and configuration

(1) Dual storage group independent configuration

Configuration independence: Bank1 and Bank2 can be set completely independently through their respective jumper groups, supporting:

Different storage types (such as Bank1 caching data in RAM and Bank2 storing programs in EPROM);

Different chip capacities (e.g. Bank 1 uses 64K x 8 chips, Bank 2 uses 128K x 8 chips);

Different backup strategies (such as using battery backup for Bank1 and no backup for Bank2);

Configuration flexibility: By combining jumper wires, flexible combinations of 8 chip capacities, 4 chip speeds, 3 backup power supplies, and 2 access permissions can be achieved without the need to modify hardware or software.

(2) Multi type storage adaptation mechanism

Requirements for storage type adaptation: Key points for jumper configuration

RAM supports static RAM chips and requires low data retention current (recommended Hitachi 6264LP-15, etc.). Enable backup power (battery or+5V STDBY) and set corresponding pin definitions for jumper wires

EPROM supports 64K/128K/256K/512K/1M capacity, TTL logic level is required to disable backup power supply, and EPROM dedicated pin definition jumper is configured

Mask ROM supports 64K/128K/256K/512K capacity with EPROM configuration, no need for backup power supply

EEPROM supports 8K × 8~32K × 8 capacity and needs to support fast write/polling technology. Disable backup power and set dedicated EEPROM pins to define jumper wires

2. Data security protection mechanism

(1) Triple Data Protection Design

First layer: Under voltage protection: Built in power monitor, when the+5V voltage is lower than 4.75V, the write function of the storage chip is automatically disabled to prevent voltage fluctuations from causing data confusion; Optionally enable SYSRESET * signal to trigger system reset to protect global data;

Second layer: Backup power supply: supports on-board battery and VMEbus+5V STDBY dual backup solution, with a typical battery backup life of 6 years, suitable for independent devices without continuous power supply; +5V STDBY backup is suitable for system level backup power scenarios;

Layer 3: Physical Protection: The pin definition jumper of the storage chip can prevent hardware damage caused by accidental insertion. In case of power failure, the write path will be automatically cut off. Combined with backup power, it ensures long-term storage of RAM data.

(2) Power monitor calibration

The power monitor has been calibrated at the factory and needs to be regularly calibrated after long-term use (recommended once a year). Calibration steps:

Place the module on the expansion board, power on, and remove the J1 jumper;

Connect the negative pole of the 4.75V reference power supply to TP2 (ground) and the positive pole to the left terminal of J1;

Connect TP1 with a multimeter or oscilloscope. If the voltage is greater than 4V, rotate the POT R3 potentiometer counterclockwise until the voltage is less than 0.8V;

Slowly rotate POT R3 clockwise until the TP1 voltage jumps to a high level and stops rotating;

Remove the reference power supply and multimeter, reinstall J1, and fix the POT R3 screw with glue to prevent loosening.

3. VMEbus compatibility and interface features

(1) Bus signal compatibility

XVME-100 fully complies with the VMEbus C.1 standard, with core compatible signals including:

Address bus: A01-A23 (A24-A31 are extended addresses), supporting a 24 bit address space;

Data bus: D00-D15, supports 8-bit/16 bit data transmission;

Control signals: AS * (address gating), DS0 */DS1 * (data gating), DTACK * (data transmission confirmation), WRITE * (read-write control), etc;

Interrupt and arbitration signals: IACKIN */ACKOUT * (interrupt response daisy chain), BUS GRANT (bus grant), BUS REQ (bus request), etc.

(2) P1 connector interface definition

The P1 connector is designed with 3 rows (A/B/C) of pins, and the core pin functions are classified as follows:

Power pin:+5 V(A32/B32/C32)、+12V(C31)、-12V(A31)、+5V STDBY(B31)、GND( Multiple pins scattered to ground);

Address pins: A01-A23 (A24-A31 located in row 2B);

Data pins: D00-D07 (A1-A8), D08-D15 (C1- C8);

Control pins: AS*(A18)、DS0*(A13)、DS1*(A12)、DTACK*(A16)、WRITE*(A14) Wait.

Installation and configuration process

1. Detailed explanation of jumper configuration

XVME-100 has a total of 52 jumpers, and the core configuration items and their corresponding relationships are as follows:

(1) Address and chip size configuration (core configuration)

Configure the target jumper position configuration logic

The Bank1 base address settings for J14 (A23) and J17-J24 (A15-A22) jumper "Out" correspond to address bit 1, and "In" corresponds to address bit 0, which needs to be set according to the system address plan

Bank1 chip size setting J50-J52 8K × 8: J50=In/J51=In/J52=In;

16K×8:J50=In/J51=In/J52=Out;

32K×8:J50=In/J51=Out/J52=In;

64K×8:J50=In/J51=Out/J52=Out;

128K×8:J50=Out/J51=In/J52=In

The basic address settings for Bank2 are J16 (A23) and J26-J33 (A15-A22), which follow the same logic as Bank1. It is necessary to avoid overlapping with the address space of Bank1

Bank2 chip size setting J47-J49 with Bank1 chip size jumper logic

(2) Other key configuration jumpers

Configuration Category Jumper Position Configuration Options

Address modifier decoding Bank1: J10-J13; Bank2: J9/J12/J15 privileged access: J13 (Bank1)/J15 (Bank2) "In" is only accessed by superusers, "Out" is accessed by all users;

Data space: J11 (Bank1)/J9 (Bank2) "In" supports data access;

Program space: J10 (Bank1)/J12 (Bank2) "In" supports program access

Chip speed selection Bank1: J6-J7; Bank2:J4-J5 100ns:Out/Out; 150ns:Out/In; 200ns:In/Out; 250ns: In/In (default)

Backup power selection J34-J35 No backup: J34=A/J35=Out (default);

Battery backup: J34=B/J35=Out;

+5V STDBY backup: J34=A/J35=In

Definition of memory chip pins Bank1: J40-J46; Bank2: J2/J3/J25/J36-J39 Select according to storage type, refer to Table 2-5 in the manual for corresponding jumper combinations

2. Installation steps and specifications

(1) Preparation before installation

Environmental verification: Confirm that the installation environment temperature and humidity meet the requirements, there are no corrosive gases, and anti-static measures are in place;

Component inspection: Check that the module has no external damage, the connector pins are not bent, and the storage chip model matches the jumper configuration;

Tool preparation: Prepare anti-static wristbands, torque screwdrivers (0.5~0.8 N · m), multimeters, and chip extractors.

(2) Installation process

Chip installation:

In the power-off state, configure the corresponding jumper according to the storage type and confirm that the chip notch direction is consistent with the slot notch;

Hand hold the edge of the chip (avoid touching the pins) and insert it evenly into the 32 pin slot, ensuring that the pins are fully in contact without bending or loosening;

Rack deployment:

Confirm that the VMEbus rack power has been turned off, align the module with the guide rail, and slowly push it in until the P1 connector is fully engaged with the backplane;

Secure the front panel of the module with M3 screws and tighten to a torque of 0.5~0.8 N · m to prevent loose screws from causing poor contact;

6U panel installation (optional):

Remove the screws and handle of the original 3U panel, and transfer the handle to the XVME-945 6U panel;

Align the mounting holes of the panel and module, fix them with screws, and ensure that the panel fits snugly with the rack;

Post installation inspection:

Use a multimeter to measure the power supply voltage of the module (+5V normal, fluctuation ≤ ± 5%);

Connect the rack power supply and observe the storage group LED light (which lights up instantly during access). If there are no abnormalities, the installation is complete.

3. Common configuration examples

Example 1: Bank1 configured with 32K × 8 EPROM, base address 8E0000 Hex

Chip size jumper (Bank1): J50=In, J51=Out, J52=In;

Base address jumper (Bank1): J14=Out (A23=1), J23=In (A22=0), J21=In (A21=0), J22=In (A20=0), J24=Out (A19=1), J20=Out (A18=1), J18=Out (A17=1), J19=A (A16=0), J17=A (A15=0);

Address space: 8E0000 Hex~8FFFF Hex (a total of 128KB, i.e. 32K × 8 × 4);

Other configurations: J13=Out (all user access), J11=In (supports data access), J10=In (supports program access), J6-J7=In/In (250ns speed), J40-J46 configured according to EPROM pin definitions.

Applicable scenarios and boundary limitations

1. Core applicable scenarios

(1) Industrial automation control

Scenario features: VMEbus architecture PLC and DCS systems require stable program storage and data caching, with large environmental temperature fluctuations and vibration interference;

Recommended configuration: Bank1 uses 64K × 8 RAM to cache real-time data (battery backup), and Bank2 uses 128K × 8 EPROM to store control programs;

Core advantages: wide temperature adaptability, strong vibration resistance, reliable data backup, and support for on-site maintenance.

(2) Military embedded devices

Scenario features: VMEbus military computer, requiring resistance to harsh environments, long lifespan, low power consumption, and storage of programs and critical data;

Recommended configuration: Bank1 uses 32K × 8 EEPROM to store key parameters (no backup), and Bank2 uses 64K × 8 RAM to cache data (battery backup);

Core advantages: Complies with military environmental standards, has a long battery backup life, and does not require frequent maintenance.

(3) Embedded System Development

Scenario features: VMEbus development platform, requiring flexible adaptation to different types of storage chips, supporting program burning and data debugging;

Recommended configuration: Bank1 uses 128K × 8 EPROM to store development programs, and Bank2 uses 128K × 8 RAM to debug data;

Core advantages: Multi type storage support, flexible jumper configuration, and the ability to switch storage modes without modifying hardware.

2. Scene boundaries and limitations

Prohibited scenarios:

High corrosion environment (such as strong acid/strong alkali workshop), without additional anti-corrosion treatment;

Extreme humidity environment (>95% RH condensation) or extreme temperature (<-40 ° C storage/-20 ° C operation);

High speed data transmission scenario (requiring storage access speed<100ns), the module supports a maximum of 100ns chips;

Performance limitations:

The maximum storage capacity of a single module is 1MB. If exceeded, multiple modules need to be expanded to avoid overlapping address spaces;

EEPROM only supports 8K × 8~32K × 8 capacity and needs to support fast write/polling technology;

Battery backup is only applicable to low-power RAM chips, and high-power RAM will significantly shorten the backup life;

Configuration restrictions:

The address space of the dual storage group needs to be aligned to the 4 x chip capacity boundary, otherwise it will cause address conflicts;

Backup power is only suitable for RAM storage, EPROM/ROM/EEPROM does not require backup and backup power jumpers need to be disabled.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- KONGSBERG

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba