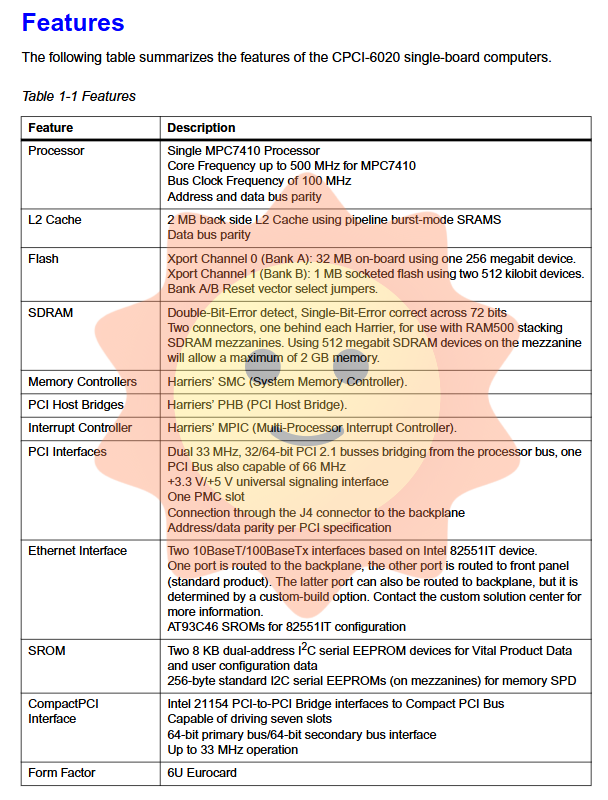

MOTOROLA CPCI-6020 CompactPCI Single Board Computer

J18-+/-12V Power Enable/Disable: Short circuiting this jumper will disable the output of all+12V and -12V power supplies on the board. If the chassis does not provide these voltages, or if the rear transition module (such as SIM card) does not require them, this jumper should be installed.

J17- Bank A Flash Block Lock Enable: After enabling, one or more blocks of Bank A Flash can be locked to prevent erasure.

J20- Bank A Flash Write Protection Enable: Once enabled, the entire Bank A Flash becomes read-only.

J19- Remote switch connector: can be connected to an external switch to achieve the same function as the ABORT and RESET buttons on the front panel.

3. Installation of daughter board:

RAM500 memory expansion module: CPCI-6020 must have at least one RAM500 module installed in order to function properly. The module is installed through the J7 and J28 connectors on the board and supports stacking up and down. During installation, align the connector and secure it with the provided screws and supports.

PMC module: During installation, it is necessary to first remove the corresponding blocking plate on the front panel, align the PMC module with the J11-J14 connectors on the board and stabilize it, and fix it with screws. In non hot swappable chassis, it must be operated in a power-off state.

CompactFlash card: Insert directly into the J15 connector on the board, paying attention to aligning Pin 1.

4. Installing the motherboard into the chassis:

Slot selection: CPCI-6020 must be installed in the CompactPCI system slot marked with a triangle symbol.

Installation steps: Open the fixed wrench on the board (note: there are multiple types of wrenches, such as Elma and Rittal), and smoothly push the board along the guide rail until the pre alignment pin contacts the backplane connector. Then close the fixing wrench until it locks, and finally tighten the fixing screws at both ends of the front panel.

Hot swappable precautions: For chassis that support hot swappable, peripheral cards can be installed or removed without the system being powered on. But before removing CPCI-6020 itself (system controller), its operating system and applications must be shut down normally through software. CPCI-6020 itself does not support hot swappable LED status and requires manual confirmation that the software has stopped.

5. Installation of the rear transition module:

CPCI-6020-MCPTM-01 needs to be installed in the corresponding slot at the back of the chassis. Important note: This module itself does not support hot swapping. Before installing or removing it, the power supply of the front-end CPCI-6020 card paired with it must be removed or turned off first. The installation process is similar to that of a motherboard, and attention should also be paid to ESD protection and mechanical alignment.

In depth analysis of system architecture and functional modules

The excellence of CPCI-6020 lies in its precise architecture design.

1. Dual Harrier ASIC core:

Two Harrier ASICs are the core hubs of the board, labeled Harrier A and B.

Harrier A: As the main bridge, it connects the processor bus to PCI Bus A. Manage most system resources, including some system memory (via memory expansion connectors), all Flash storage NVRAM/RTC、 On board I2C EEPROM, two UART, and bridging to all devices on PCI Bus A (such as 21154 PCI to PCI bridge, main Ethernet, PCI/ISA bridge). It is also responsible for top-level interrupt control.

Harrier B: Connect the processor bus to PCI Bus B. Mainly manages another part of the system memory and provides bridging and interrupt control for PCI Bus B (PMC slots and secondary Ethernet controllers).

This discrete design enhances I/O bandwidth and system reliability.

2. Memory subsystem:

The memory is fully provided by the RAM500 expansion module, which is connected to Harrier A and B through two independent 72 bit wide (64 bit data+8-bit ECC) buses. The ECC function can correct single bit errors, detect double bit errors, and greatly improve data integrity. The memory size can be flexibly configured by installing RAM500 modules of different capacities.

3. PCI bus structure:

PCI Bus A (33 MHz): Provides a local CompactPCI bus that complies with the CompactPCI 2.0 specification through the Intel 21154 PCI to PCI bridge chip, capable of driving up to 7 peripheral slots. At the same time, the bus is also connected to Winbond W83C554F PCI/ISA bridge (providing EIDE and ISA bus functions), main Ethernet controller, NEC USB host controller, as well as Zilog ESCC and CIO chips for synchronizing serial ports.

PCI Bus B (33/66 MHz): specifically designed to serve PMC expansion slots and secondary Ethernet controllers. Its operating frequency is determined by the automatic detection of the M66EN pin status of the installed PMC module (which can be covered by J21 jumper). If a 66MHz PMC is detected, the bus will run at 66MHz and the secondary Ethernet controller will be disabled (as it only supports 33MHz).

4. High availability support:

CPCI-6020 communicates with the bridge board in Motorola HA chassis through J4 connector to achieve hot plugging and fault switching of system slots. The mechanism includes:

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba