XYCOM XVME-100 memory module

Power pin:+5 V(A32/B32/C32)、+12V(C31)、-12V(A31)、+5V STDBY(B31)、GND( Multiple pins scattered to ground);

Address pins: A01-A23 (A24-A31 located in row 2B);

Data pins: D00-D07 (A1-A8), D08-D15 (C1- C8);

Control pins: AS*(A18)、DS0*(A13)、DS1*(A12)、DTACK*(A16)、WRITE*(A14) Wait.

Installation and configuration process

1. Detailed explanation of jumper configuration

XVME-100 has a total of 52 jumpers, and the core configuration items and their corresponding relationships are as follows:

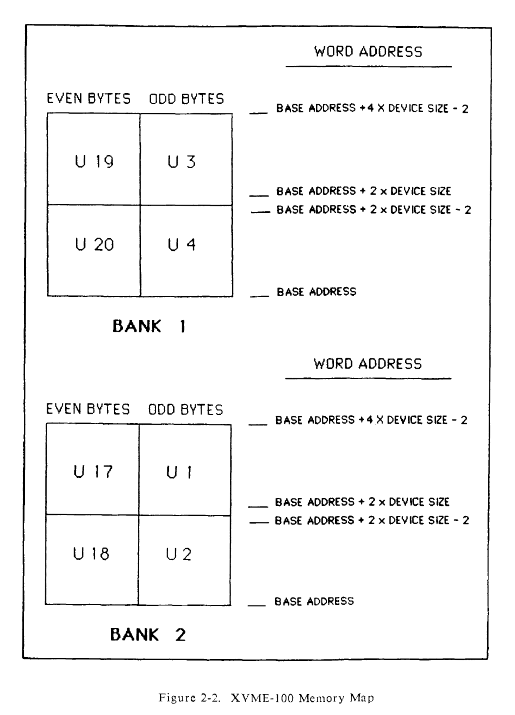

(1) Address and chip size configuration (core configuration)

Configure the target jumper position configuration logic

The Bank1 base address settings for J14 (A23) and J17-J24 (A15-A22) jumper "Out" correspond to address bit 1, and "In" corresponds to address bit 0, which needs to be set according to the system address plan

Bank1 chip size setting J50-J52 8K × 8: J50=In/J51=In/J52=In;

16K×8:J50=In/J51=In/J52=Out;

32K×8:J50=In/J51=Out/J52=In;

64K×8:J50=In/J51=Out/J52=Out;

128K×8:J50=Out/J51=In/J52=In

The basic address settings for Bank2 are J16 (A23) and J26-J33 (A15-A22), which follow the same logic as Bank1. It is necessary to avoid overlapping with the address space of Bank1

Bank2 chip size setting J47-J49 with Bank1 chip size jumper logic

(2) Other key configuration jumpers

Configuration Category Jumper Position Configuration Options

Address modifier decoding Bank1: J10-J13; Bank2: J9/J12/J15 privileged access: J13 (Bank1)/J15 (Bank2) "In" is only accessed by superusers, "Out" is accessed by all users;

Data space: J11 (Bank1)/J9 (Bank2) "In" supports data access;

Program space: J10 (Bank1)/J12 (Bank2) "In" supports program access

Chip speed selection Bank1: J6-J7; Bank2:J4-J5 100ns:Out/Out; 150ns:Out/In; 200ns:In/Out; 250ns: In/In (default)

Backup power selection J34-J35 No backup: J34=A/J35=Out (default);

Battery backup: J34=B/J35=Out;

+5V STDBY backup: J34=A/J35=In

Definition of memory chip pins Bank1: J40-J46; Bank2: J2/J3/J25/J36-J39 Select according to storage type, refer to Table 2-5 in the manual for corresponding jumper combinations

2. Installation steps and specifications

(1) Preparation before installation

Environmental verification: Confirm that the installation environment temperature and humidity meet the requirements, there are no corrosive gases, and anti-static measures are in place;

Component inspection: Check that the module has no external damage, the connector pins are not bent, and the storage chip model matches the jumper configuration;

Tool preparation: Prepare anti-static wristbands, torque screwdrivers (0.5~0.8 N · m), multimeters, and chip extractors.

(2) Installation process

Chip installation:

In the power-off state, configure the corresponding jumper according to the storage type and confirm that the chip notch direction is consistent with the slot notch;

Hand hold the edge of the chip (avoid touching the pins) and insert it evenly into the 32 pin slot, ensuring that the pins are fully in contact without bending or loosening;

Rack deployment:

Confirm that the VMEbus rack power has been turned off, align the module with the guide rail, and slowly push it in until the P1 connector is fully engaged with the backplane;

Secure the front panel of the module with M3 screws and tighten to a torque of 0.5~0.8 N · m to prevent loose screws from causing poor contact;

6U panel installation (optional):

Remove the screws and handle of the original 3U panel, and transfer the handle to the XVME-945 6U panel;

Align the mounting holes of the panel and module, fix them with screws, and ensure that the panel fits snugly with the rack;

Post installation inspection:

Use a multimeter to measure the power supply voltage of the module (+5V normal, fluctuation ≤ ± 5%);

Connect the rack power supply and observe the storage group LED light (which lights up instantly during access). If there are no abnormalities, the installation is complete.

3. Common configuration examples

Example 1: Bank1 configured with 32K × 8 EPROM, base address 8E0000 Hex

Chip size jumper (Bank1): J50=In, J51=Out, J52=In;

Base address jumper (Bank1): J14=Out (A23=1), J23=In (A22=0), J21=In (A21=0), J22=In (A20=0), J24=Out (A19=1), J20=Out (A18=1), J18=Out (A17=1), J19=A (A16=0), J17=A (A15=0);

Address space: 8E0000 Hex~8FFFF Hex (a total of 128KB, i.e. 32K × 8 × 4);

Other configurations: J13=Out (all user access), J11=In (supports data access), J10=In (supports program access), J6-J7=In/In (250ns speed), J40-J46 configured according to EPROM pin definitions.

Applicable scenarios and boundary limitations

1. Core applicable scenarios

(1) Industrial automation control

Scenario features: VMEbus architecture PLC and DCS systems require stable program storage and data caching, with large environmental temperature fluctuations and vibration interference;

Recommended configuration: Bank1 uses 64K × 8 RAM to cache real-time data (battery backup), and Bank2 uses 128K × 8 EPROM to store control programs;

Core advantages: wide temperature adaptability, strong vibration resistance, reliable data backup, and support for on-site maintenance.

(2) Military embedded devices

Scenario features: VMEbus military computer, requiring resistance to harsh environments, long lifespan, low power consumption, and storage of programs and critical data;

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- KONGSBERG

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba