YASKAWA MEMOCON-SC 2000 series reversible counter module

Reset logic: When the external reset or current value reset signal is ON, the count stops and clears to zero

(3) Ladder diagram configuration

Core parameters: Coincidence preset value=1000, count width=2000 (maximum value 999999 in GL20 6-digit mode)

Counting process: ADD count up to 1000 → Coincidence output ON → Continue counting up to 2000 → Auto reset → Repeat loop

3. Sampling Counter

(1) Core functions

Basic ability: When receiving external sampling signals, latch the current count value and store it in the designated input register

Storage allocation: Counter 1 data is stored in input registers 1-2; Counter 2 data is stored in input registers 3-4

Sampling control: The sampling frequency can be reset through the "output disable" signal

(2) Key parameters

Sampling period: T ≥ 10ms, and must meet T ≤ (2 ¹⁹ -1)/(f · k) (GL20) or T ≤ (2 Ω³ -1)/(f · k) (GL60S), where f is the input pulse frequency and k is the magnification ratio

Signal requirements: Sampling signal ON response time<1ms, OFF response time<2ms, pulse width ≥ 5ms

(3) Operational logic

Initial state: When switching to sampling counter mode, the current value and carry/borrow flag are reset to zero

Data update: When the current value is preset, the sampled value is synchronously updated to the preset value

4. Memory Counter

(1) Core functions

Basic ability: When triggered by external sampling signals, latch the current count value and store it in the built-in data memory in the order of reception (up to 999 sets of data can be stored)

Data reading: By specifying the address through the "pointer command", the corresponding stored data can be read from the input register

Coincidence output: When the amount of stored data reaches the preset value, output a coincidence ON signal

(2) Key parameters

Storage limit: Stop sampling after the storage capacity reaches 999; When the preset value is 0, no coincidence signal is output

Sampling period: As required by the sampling counter (T ≥ 10ms, meeting frequency related constraints)

Read latency: After the local I/O pointer command is turned on, the data read latency is ≤ 3 scan cycles; Remote I/O ≤ 5 scanning cycles

(3) Operational logic

Reset control: When the "output disable" signal is turned on, the stored data is reset to zero, the storage count is reset, and the coincidence output is turned off

Pointer feature: When the pointer command is OFF, the input register displays the current count value; Display data stored at the specified address when turned on

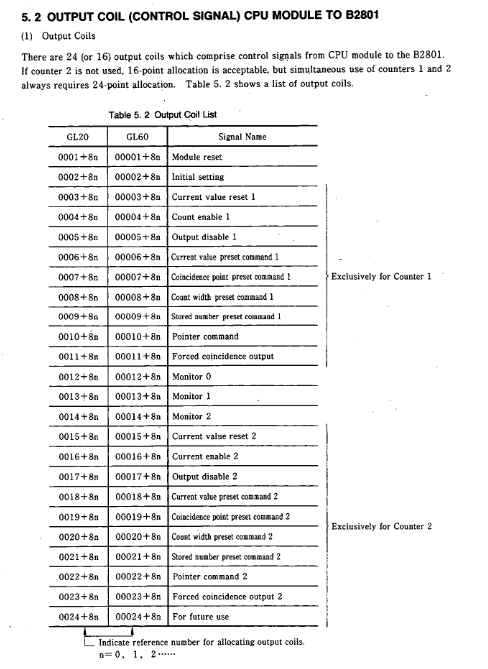

Internal interface and signal definition

1. I/O allocation (interaction between CPU and B2801)

Interface type allocation specification signal flow direction

Output coil 24 points (dual counter)/16 points (single counter) CPU → B2801 (control signal)

Input relay 16 points (dual counter)/8 points (single counter) B2801 → CPU (status signal)

4 output registers (binary allocation) CPU → B2801 (set data)

4 input registers (binary allocation) B2801 → CPU (monitoring data)

2. Core control signal (output coil)

Signal Name Function Description Effective Methods

Module reset initializes internal RAM and external I/O signals, and the counter returns to its default value, triggering OFF → ON

Initial setting: Configure the counter function mode (compare/cycle/sample/store) OFF → ON trigger (count enable needs to be OFF)

Count enable, in conjunction with an external enable signal (ENB), allows the counter to count ON effectively

Output disable: Disable coincidence output or reset coincidence signal ON to be effective

The preset command (Current/Consensus/Count width preset) sets the current value, coincidence point, and count width OFF → ON trigger

Pointer command stores counter data, reads address specified ON is valid

3. Status feedback signal (input relay)

Signal Name Function Description Status Definition

READY module self diagnosis result (ROM/RAM/WDT check) ON=normal; OFF=abnormal

Preset ACK/NAK preset operation completion status feedback ACK=successful; NAK=Failed

Carry/Borrow count overflow feedback ON=1 scan cycle (compare/loop mode); Storage data overflow (sampling/storage mode)

Coincidence output - Coincidence signal output status feedback ON=coincidence condition satisfied

Scanning time error: CPU scanning time too short ON=error; OFF=Normal

4. Definition of Register Data

(1) Output register (set data)

1-2: Counter 1 dedicated (pulse mode, counting multiplier, coincidence mode, function selection, preset value, etc.)

3-4: Counter 2 dedicated (same as counter 1 configuration item)

Data range: GL20 (3-digit decimal); GL60S (4-digit decimal)

(2) Input register (monitoring data)

1-2: Counter 1 monitoring (current value, sampled value, stored data, etc.)

3-4: Monitoring of counter 2 (same as monitoring item of counter 1)

Monitoring mode: Switch through the combination of "Monitor 0~2" (e.g. 0-0-0=current value; 0-1-1=sampling times)

External interface and terminal connection

1. Front panel layout

LED indicator lights: RDY (self diagnostic status), 1ENB/2ENB (counting enabled), 1PHA/2PHA (phase A input), 1PHB/2PHB (phase B input), 1INC/2INC (addition counting), 1DEC/2DEC (subtraction counting), 1EQU/2EQU (coincidence output), 1ERR/2ERR (error alarm)

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- KONGSBERG

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba