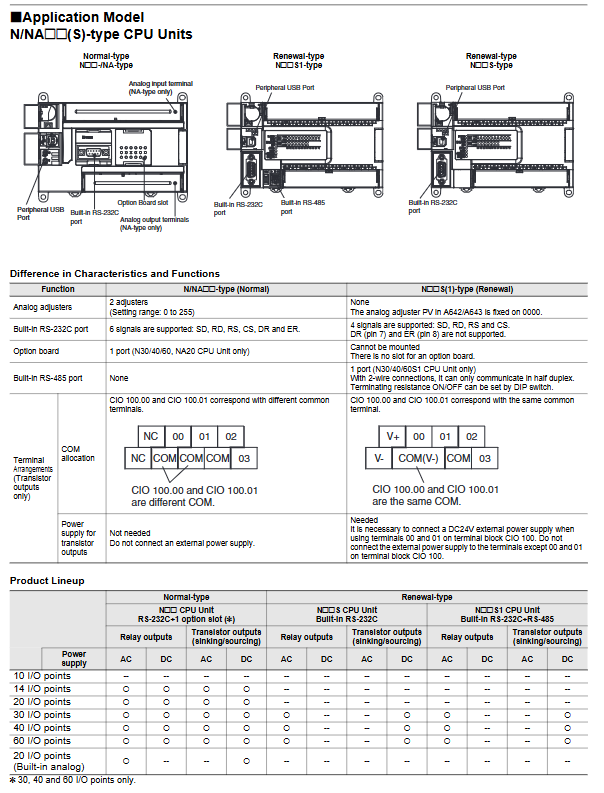

OMRON CP1E PLC Practical Selection Guide

Changing the target value during execution only supports changing the target position

Origin search support

PWM output (CIO 100.01):

Frequency range: 2.0~6553.5Hz (step size 0.1Hz) or 2Hz~32000Hz (step size 1Hz)

Duty cycle: 0.0%~100.0% (step size 0.1%)

Accuracy:+1%/-0% at 2~10kHz,+5%/-0% at 10~32kHz

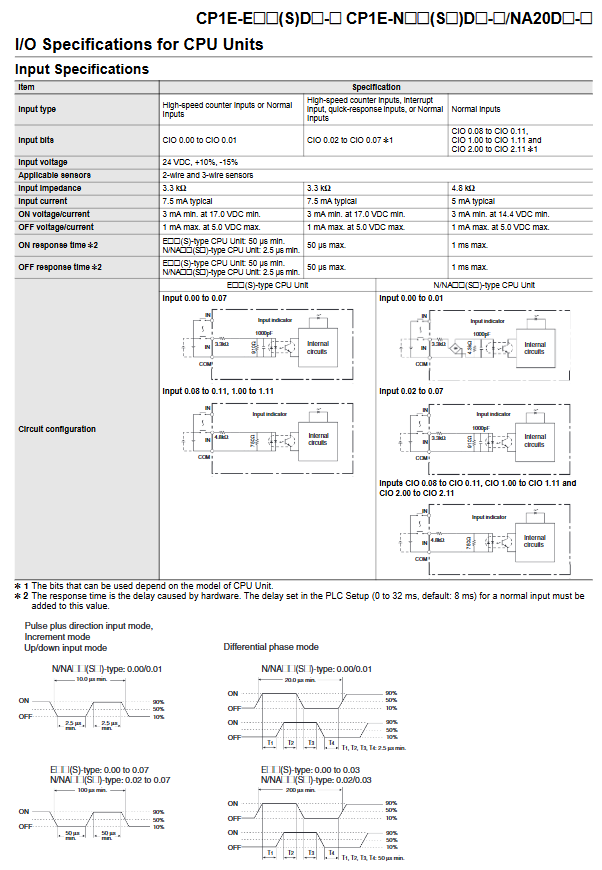

3.3 Interruption and Fast Response Input

Input interrupt: 6 o'clock (10 o'clock CPU is 4 o'clock), minimum pulse width 50 μ s

Fast response input: 6-point (4-point CPU at 10pm), minimum pulse width of 50 μ s

Timed interrupt: 1 task

High speed counter interrupt: 16 tasks

Memory Structure and Data Backup

4.1 I/O Memory Area

Description of Regional Address Range Size

CIO area (input) CIO 0~99 100 words Built in input occupies CIO 0, automatic allocation of expansion units

CIO area (output) CIO 100~199 100 word built-in output occupies CIO 100, NA type analog output occupies CIO 190

Serial PLC link area CIO 200~289 90 words for data exchange between CPUs

Work area (W) W0~W99 100 word internal auxiliary relay

Hold zone (H) H0~H49 50 word power-off hold (battery required)

Auxiliary area (A) A0~A447 (read-only), A448~A753 (read-write) 960 word system flag and status

Timer (T) T0~T255 256 point timer

Counter (C) C0~C255 256 point counter (battery required for power-off maintenance)

Data memory (D) E-type: D0~D2047; N-type: D0~D8191 2K/8K word data storage

4.2 Memory backup mechanism

The CP1E CPU unit adopts a dual layer structure of built-in RAM (execution memory) and built-in EEPROM (backup memory):

User program: automatically saved to EEPROM during writing

Parameter area: automatically saved to EEPROM

DM area data: The specified range (E-type D0~D1499, N-type D0~D6999) can be saved to EEPROM through A751.15 (DM backup save boot bit). After setting the "Restore D0 from Backup Memory" checkbox in PLC Setup, it will automatically restore when powered on.

Battery backup (CP1W-BAT01, N/NA type only): used to maintain the hold area (H), counter (C), partial DM area, auxiliary area, and clock. Battery life: about 1.5 years at 55 ℃ and about 5 years at 25 ℃. When there is no battery, the built-in capacitor can hold for about 40 hours (N/NA type).

Engineering Tip: The DM area (D1500~D2047) of E-type without battery and EEPROM backup will become unstable after the capacitor retention time (about 50 hours) is exceeded due to power failure. The program should avoid storing critical data in this area.

Built in analog quantity (NA type)

The NA20 CPU unit is equipped with 2 analog inputs and 1 analog output:

5.1 Analog Input

Project voltage input current input

Input range: 0~5V, 1~5V, 0~10V, -10~10V, 0~20mA, 4~20mA

Resolution 1/6000 1/6000

Accuracy (25 ℃) ± 0.3% Full Scale ± 0.3% Full Scale

Accuracy (0~55 ℃) ± 0.6% full-scale ± 0.6% full-scale

Convert data -10~10V: F448~0BB8 Hex; Other: 0000~1770 Hex

Input the words CIO 90, CIO 91-

5.2 Analog output

Project voltage output current output

Output range: 0~5V, 1~5V, 0~10V, -10~10V, 0~20mA, 4~20mA

Resolution 1/6000 1/6000

Accuracy (25 ℃) ± 0.4% full-scale -

Accuracy (0~55 ℃) ± 0.8% full-scale -

Convert data to input -

Output word CIO 190-

Equalization function: Supports (can be set separately for each input in PLC Setup).

Wire breakage detection: supported (data is 8000 Hex when wire breakage occurs).

Detailed explanation of communication interface

6.1 Built in communication port

CPU model USB port RS-232C port RS-485 port option board slot

Type E (Type B) None None None None

N14/20 present (full signal) none none

N □ S type Yes (4-wire) No No

N □ S1 type Yes (4 wires) Yes (2 wires) No

N30/40/60/NA20 Yes (full signal) No 1

USB Port: Compliant with USB 2.0 Type B, with a transfer distance of 5m. Can be connected to CX Programmer using a commercial USB cable (Type-B).

Built in RS-232C port:

Compliant with EIA RS-232C standard, half duplex start stop synchronization

Baud rate: 1.2/2.4/4.8/9.6/19.2/38.4/57.6/115.2 kbps

Transmission distance: 15m

Supporting protocols: Host Link, 1: N NT Link, no protocol, serial PLC link (master/slave), Modbus RTU simple master station

Built in RS-485 port (N □ S1 type):

2-wire system, half duplex, non isolated

Same baud rate as above, transmission distance 50m

The terminal resistor can be set ON/OFF through DIP switches

Supporting the same agreement as above

6.2 Option board (N30/40/60/NA20 type)

Model Interface Isolation Transmission Distance Description

CP1W-CIF01 RS-232C-15m D-sub 9-pin female head

CP1W-CIF11 RS-422A/485 non isolated 50m terminal block

CP1W-CIF12-V1 RS-422A/485 isolated 500m terminal block

CP1W-CIF41 Ethernet -100m RJ45100/10Base TX, Auto MDIX, requires CX Programmer 9.12 or higher

Attention: CP1W-CIF41 requires version 2.0 or higher, and CP1E CPU unit version 1.2 or higher.

Expansion Unit and I/O Configuration

7.1 Expansion of I/O Unit

Model Input/Output Type 5V Current 24V Current

CP1W-8ED 8 0 — 0.018A —

CP1W-8ER 0 8 relay 0.026A 0.044A

CP1W-8ET 0 8 transistor (sinking) 0.075A -

CP1W-16ER 0 16 relay 0.042A 0.090A

CP1W-32ER 0 32 relay 0.049A 0.131A

CP1W-20EDR1 12 8 relay 0.103A 0.044A

CP1W-40EDR 24 16 relay 0.080A 0.090A

Relay output derating:

CP1W-8ER/16ER/20EDR1/40EDR: When the ambient temperature exceeds 50 ℃, the current at each common terminal needs to be reduced to below 0.9A (originally 1.2A or 2A).

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba