Rockwell Automation SLC 500 Series Programmable Logic Controller

Rockwell Automation SLC 500 Series Programmable Logic Controller

Introduction: The classic cornerstone of industrial automation

In the field of industrial automation, the Allen Bradley SLC 500 series programmable logic controller (PLC) occupies an indelible historical position. As a key bridge connecting early relay control systems with modern complex networked control, SLC 500 not only demonstrates extremely high reliability in hardware, but its instruction set system also lays the foundation for programming concepts on subsequent platforms such as ControlLogix. This article is based on the 1747-RM001G-EN-P reference manual and aims to provide an in-depth analysis of the core instruction system of SLC 500, from the underlying data architecture to advanced closed-loop control, providing automation engineers with a highly practical and valuable professional guide.

Chapter 1: The underlying logic of processor file architecture

To master SLC 500 programming, the primary task is to understand its memory architecture. The user memory of SLC 500 is strictly divided into two categories: data files and program files. This structured design ensures efficient addressing and secure isolation of data.

1. Fine division of data files

The data file numbers range from 0 to 255, and the system assigns specific file types by default:

I/O Image Area (File 0&1): File 0 is the output image, and File 1 is the input image. Its addressing format strictly follows the structure of O: e.s/b or I: e.s/b. Among them, e represents the physical slot number, s represents the word address (for modules with more than 16 I/O points), and b represents the bit number. This method of directly binding physical location with logical address greatly facilitates on-site wiring verification.

Status file (File 2, S:): This is the "black box" of the processor, which records key information such as system clock, error codes, communication status, etc. For example, S: 1/15 is the first scan bit, commonly used for system initialization; S: 5/0 is a math overflow trap bit, if not reset in time, it will cause the processor to crash.

Data storage area (File 3-8): The default configuration includes bit files (B3), timers (T4), counters (C5), controls (R6), integers (N7), and floating-point numbers (F8). It is particularly noteworthy that the timer and counter are a 3-bit element structure, containing control words, preset values (PRE), and cumulative values (ACC), respectively. This composite structure requires special attention to the difference between word addressing and bit addressing during programming.

2. Hierarchical management of program files

File 2 is the main program, and files 3 to 255 are subroutines. Through this division, engineers can decouple complex process logic into independent modules, enabling code reuse and maintenance.

Chapter 2: Fine Control Mechanism of Basic Instructions

The basic instructions form the backbone of ladder logic, but in SLC 500, seemingly simple instructions hide strict timing and state preservation mechanisms.

1. The combination of virtual and real logic

XIC (check for closure) and XIO (check for disconnection) are not simply reading physical states, but checking for "logic 1" or "logic 0" in the data table. This means that if a physically disconnected button (input 0) is latched (OTL) to 1 in the program, the XIC instruction will still be judged as true. OTE (Output Excitation) is non hold type, and its state will be reset if it is in the MCR (Main Control Reset) disabled area or power off; OTL (latch) and OTU (unlock) have retention characteristics, which require extreme caution in safety circuit design.

2. Three forms of timers

TON (Connection Delay): The most commonly used timer that starts counting when the step condition is true, and when the preset value is reached, the Done bit (DN) is placed. When the condition becomes false, it is immediately reset.

TOF (disconnection delay): Timing starts when the step conditions become false. Engineering Pit Avoidance Guide: Never use RES (Reset) command to reset TOF, as RES will clear all status bits, causing timing confusion.

RTO (Hold Timer): Even if the step conditions become false or power is lost (with battery backup), the accumulated value will be maintained. It must be manually reset through the RES command, which is commonly used to record the accumulated running time of the device.

3. Counter and high-speed pulse processing

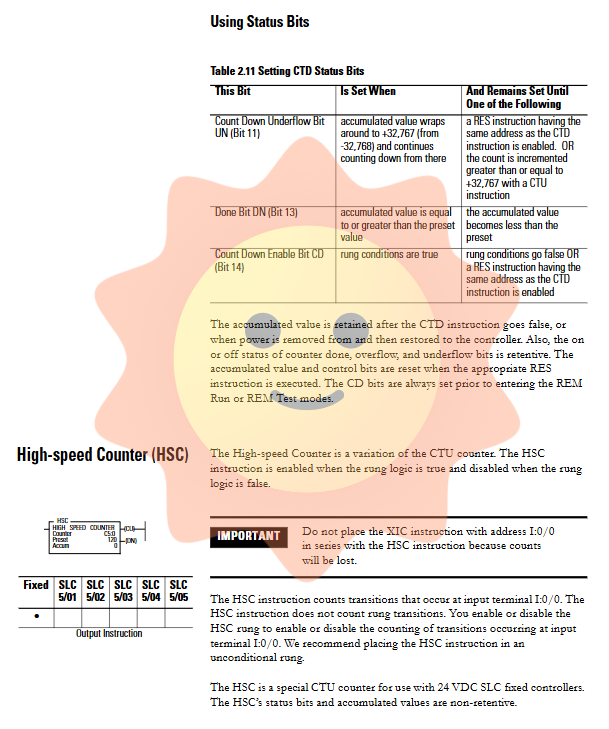

CTU (up counting) and CTD (down counting) are triggered along the transition edge from false to true in the cascade. When the count value exceeds+32767, the overflow bit (OV) is set and the value becomes -32768, which is a characteristic of signed integer complement. For the fixed SLC 500, the HSC (high-speed counter) instruction allows direct processing of hardware pulses up to 8kHz, but this requires physically disconnecting the J2 jumper inside the controller, configuring I: 0/0 as high-speed input mode, and asynchronous delay between its software accumulation value and hardware count value.

Chapter 3: Advanced Applications of Data Operations and Comparisons

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- KONGSBERG

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba