Saia PCD4.U100 Kit System Upgrade Guide

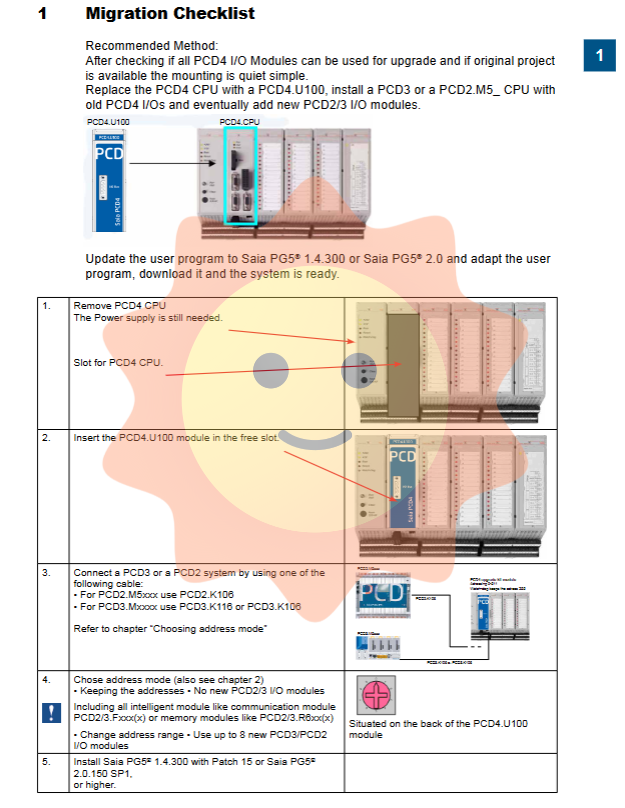

However, a comprehensive replacement of the control system often means high costs and long downtime. Saia Burgess Controls (SBC) has launched the PCD4.U100 migration kit to address this pain point. This innovative solution allows users to upgrade the core processing unit to a more powerful PCD2.M5xxx or PCD3.Mxxxx series CPU while retaining the original PCD4 I/O module. This article will provide you with a detailed analysis of the hardware installation, address mode configuration, software migration process, and professional technical details of the PCD4.U100 suite based on official technical documents, and offer you a comprehensive operation guide.

Cost: The original user program needs to address adjust all I/O access instructions by adding 256 to the original address. At the same time, the PCD4 watchdog address has also shifted from 255 to 511 (or higher).

Applicable scenarios: It is hoped that while upgrading the CPU, new I/O modules or communication modules can be expanded to enhance system functionality.

2.3 Dual handling of watchdog

The manual specifically mentions the issue of Watchdogs. In the PCD4 system, the watchdog address is usually located at 255 and 511. On the new CPU, the watchdog address is 255. When selecting the "Address Offset 256" mode, the address of the PCD4 watchdog changes to 511 (old watchdog address offset) and 767, distinguishing it from the CPU's built-in watchdog (address 255). This detail needs special attention when writing and maintaining diagnostic programs.

Part Three: Serial Communication and Differences between New and Old Systems

Hardware upgrades inevitably bring about some functional changes that require engineers to adapt at the software level.

3.1 Serial Communication Port

The serial communication port (such as RS-232) on the original PCD4 CPU is no longer available in the new system. All communication functions will be provided by the onboard serial port on the new PCD2/3 CPU or through the newly added PCD2/3. Fxxx communication module. Therefore, during the migration process, it is necessary to remap the operations on the old CPU serial port in the original program to the new communication port.

3.2 Changes in Key XOB Organizational Blocks

XOB is an organizational block in PCD systems that handles specific events (similar to interrupt programs).

XOB 5: In the original system, XOB 5 was used to process I/O exit (/IOQUIT) signals. The manual clearly states that in the new generation CPU, this signal no longer exists, so XOB 5 is no longer valid. All code related to XOB 5 should be commented out.

XOB 1: XOB 1 is used to detect power failures on the I/O bus. The manual states that in the new system, when a power failure is detected in the PCD4 I/O bus or expansion module (such as PCD3. C200), XOB 1 will be triggered, but the detection time is approximately 500ms. More importantly, it compares the differences in fault detection capabilities between the old and new PCD4 power modules (N200 and N210), such as N210 being able to simultaneously monitor+5V and ± 15V outputs, while N200 cannot detect ± 15V. This reminds engineers that the diagnostic ability of the upgraded system for power failures may change and needs to be considered in the program.

Part Four: User Program Migration and Adaptation

This is the most labor-intensive and technically advanced part of the entire upgrade project. The user program must adapt to the high-speed performance of the new CPU and different hardware architectures.

4.1 Fupla Programming Method

For users who use Fupla (functional block diagram) for programming, the adaptation process is relatively simple.

Prerequisite: Use Saia PG5 ® 1.4.300 Patch 15 or 2.0.150 SP1 and above versions.

Required libraries: Ensure that the latest versions of the "Analogue Module" and "HVC Analogue" libraries are installed.

Automatic update: In PG5 2.0, an activation tool needs to be run to enable PCD4 I/O FBoxes. Afterwards, when opening the old project, all function blocks (FBox) related to PCD4 I/O will be automatically updated to a version compatible with PCD4.U100.

4.2 Deep adaptation of IL programming method

For engineers who use instruction lists (ILs) for programming, the adaptation process is more critical and requires manual or semi manual modification of the code.

4.2.1 Critical 2-second startup delay

Due to the significantly higher processing speed of the new CPU compared to the old PCD4 CPU, a direct issue is that external PCD4 I/O modules may not have completed their own initialization when the new CPU is powered on and starts executing programs. This can cause the I/O module to not be configured correctly, resulting in system failures.

Solution: At the beginning of the program, a delay of at least 2 seconds must be enforced. The manual provides detailed implementation steps:

Create a new. src file (such as Wait_2s. src).

Write the following IL code in this file to implement an accurate 2-second delay loop:

text

$WAITFOR ; Wait for timer to start

BEGIN

SET 8 1 ; Set up a timer for 2 seconds (depends on system tick)

; . .. (For specific timing cycle codes, please refer to the original manual)

END

Key step: In the Link Order setting of the project, the newly created Wait_2s.src file must be placed at the top of the link list. Ensure that it is executed before any other user program code.

This operation ensures that the program will first execute a 2-second wait during each CPU startup or cold start, giving the PCD4 I/O module sufficient initialization time.

4.2.2 Code adaptation for specific modules

In addition to the global startup delay, some I/O modules (such as PCD4. W100, W500, W600) require additional null operation (NOP) instructions to be inserted under high-speed CPUs due to their operational characteristics to ensure timing accuracy.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- KONGSBERG

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba