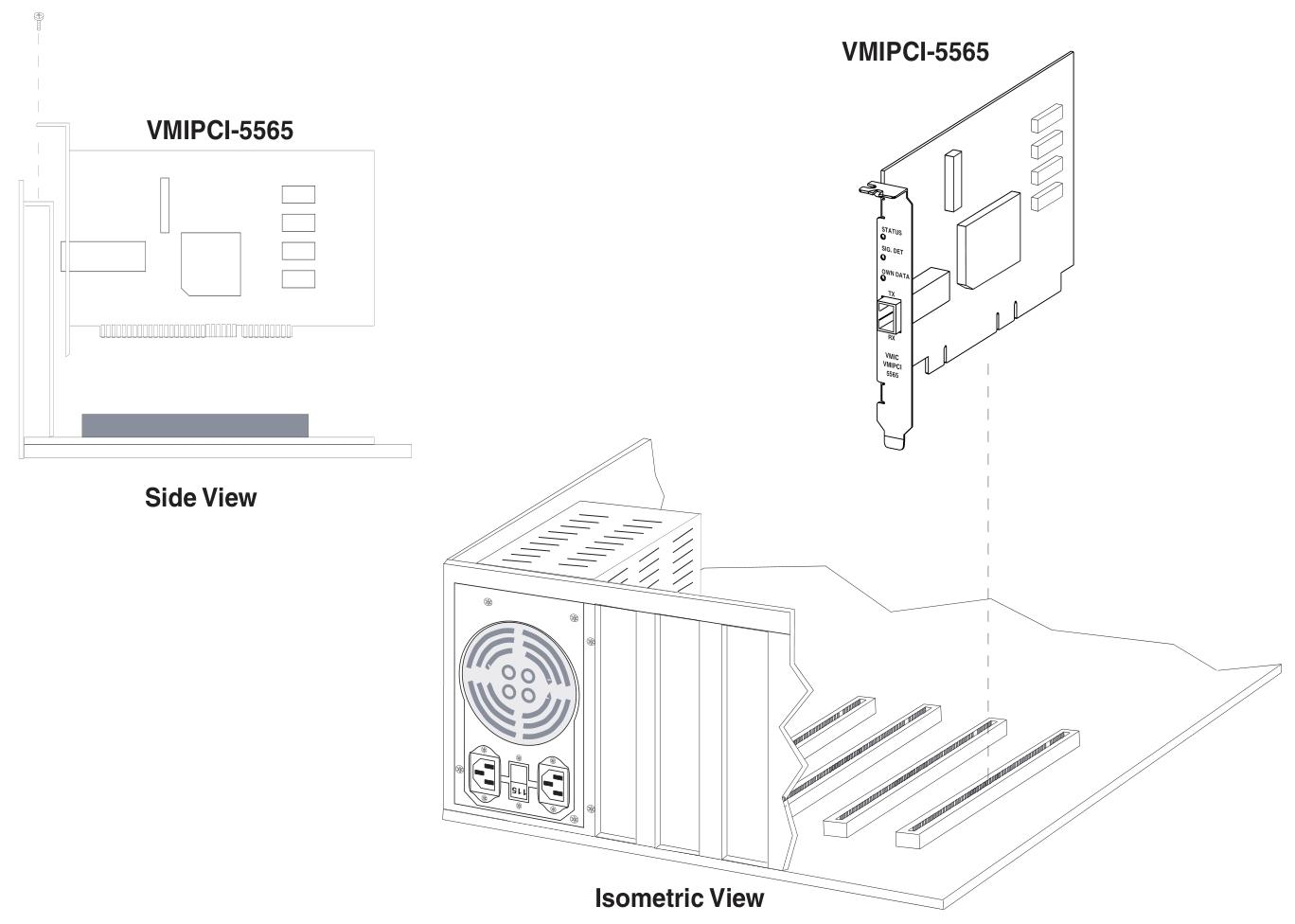

GE VMIPCI-5565 Ultrahigh Speed Fiber-Optic Reflective Memory with Interrupts

Cable configuration: Provides cable specifications and connector specifications for multimode or single-mode fiber optic interfaces, including core diameter, cladding diameter, sheath outer diameter, attenuation, bandwidth, and other parameters, as well as connector compatibility, insertion loss, and other information.

Connectivity: Nodes are connected in a circular manner, as in the example of a circular connection of six nodes.

Programming

PCI configuration register: located in the 256 bytes of the PCI configuration space, the first 64 bytes are predefined headers that contain information such as vendor ID and device ID. Some registers can be modified by the user, while others are read-only or initialized by the system BIOS.

Local configuration registers: can be accessed through base address register offset 0 or 1, initialized to normal working configuration by serial EEPROM, and some registers can be modified by users to match the host system.

Runtime register: It is also accessed through the base address register offset 0 or 1, and will not be initialized by the serial EEPROM, maintaining the default state when the PCI bus is reset. Users need to modify some bits to activate the desired operating mode.

DMA control register: accessed through offset 0 or 1 of the base address register, it defaults to the PCI reset state and needs to be modified by the user to activate the operating mode, including DMA channel mode register, address register, etc., used to operate two DMA engines.

RFM control and status register: located in PLX local address space 0, the base address is specified by "PCI base address 2" in the PCI configuration register, including board revision register, node ID register, etc., to achieve the unique function of reflecting the memory board.

DMA operation example: It is necessary to find the value of the base address register 0, set five DMA registers, and then start the transfer and monitor the completion status by writing to the command/status register.

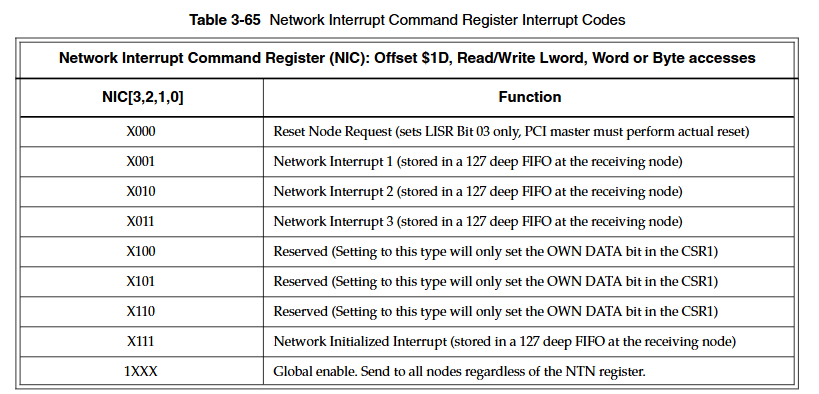

Example of network interrupt handling: including setting steps (clearing previous interrupts in FIFO, setting relevant registers to enable interrupts, etc.) and steps for serving network interrupts (reading registers to determine interrupt source, processing data and sender ID, etc.).

Maintain and comply with information

Maintenance: When the product malfunctions, it is necessary to first check the software, system configuration, electrical connections, etc. If a return is required, please contact GE Fanuc Embedded Systems to obtain a Return Merchandise Authorization (RMA) number. User level repairs are not recommended, and the drawings and charts in the manual are for reference only.

Compliance information: Complies with multiple international standards and regulations, such as the EU's EN series standards, the US FCC Part 15, and Australia/New Zealand's AS/NZS CISPR 22. Compliance requirements and restrictions vary in different regions.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba