GE VMIPCI-5565 Ultrahigh Speed Fiber-Optic Reflective Memory with Interrupts

GE VMIPCI-5565 Ultrahigh Speed Fiber-Optic Reflective Memory with Interrupts

Product Overview

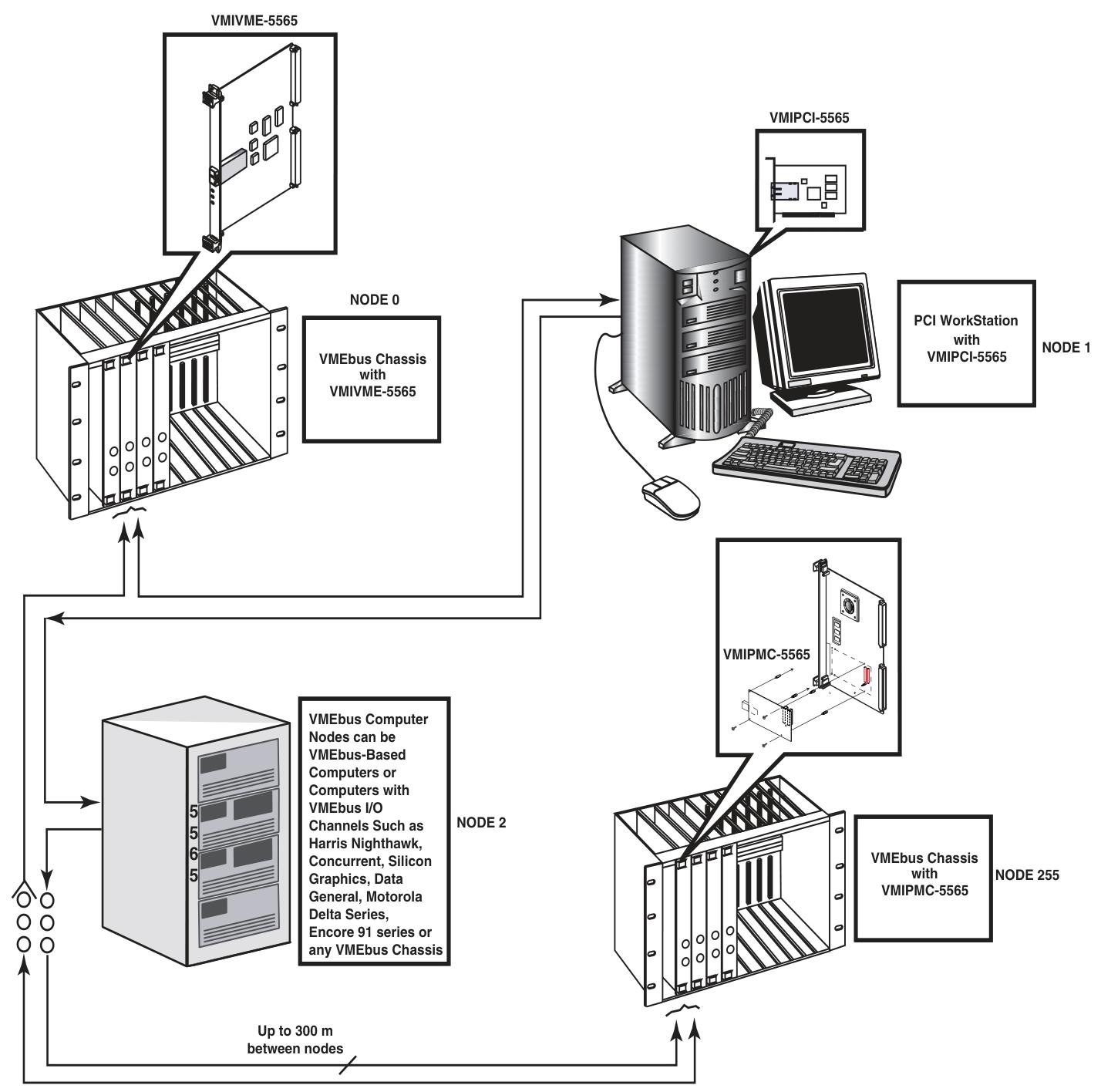

Basic information: VMIPCI-5565 is a PCI based reflective memory real-time fiber optic network product for GE Fanuc embedded systems, belonging to the VMIxxx-5565 series. It can be integrated into the network with other members of the series through standard fiber optic cables, and each board is called a node, allowing computers and other devices with different architectures and operating systems to share data in real time.

Key Features

A high-speed and easy-to-use fiber optic network with a serial rate of 2.12 Gbaud.

Supports PCI 64 bit 66MHz transmission, network operation does not require the involvement of a host processor.

Equipped with redundant operation mode, supporting up to 256 nodes.

The multi-mode fiber optic connection distance can reach up to 300 meters, and the packet size is dynamically variable (4-64 bytes).

The transmission rate varies depending on the packet size, with 47.1MB/s for 4-byte packets and 174MB/s for 64 byte packets.

Equipped with 64MB or 128MB SDRAM reflective memory with parity check, as well as two independent direct memory (DMA) channels, configurable byte order conversion to accommodate multiple CPU architectures on the same network.

Operating principle

Basic operation: Each node in the network is interconnected in a daisy chain loop through fiber optic cables, and each node needs to have a unique node ID (set through 8 onboard jumpers). The data transmission is initiated by the PCI host system writing data to the onboard SDRAM. During the writing process, the onboard circuit automatically writes the data and related information into the transmit FIFO, forming variable length data packets that are transmitted through the fiber optic interface. The receiver opens the data packet and stores it in the receive FIFO, then writes it into the local SDRAM and routes it to its own transmit FIFO until the data returns to the source node and is removed.

Register group: including PCI configuration registers, local configuration registers, runtime registers, DMA control registers, reflective memory (RFM) control and status registers. The functions and purposes of each register group are different, and some registers have different initialization methods and modification frequencies.

Reflective memory RAM: There are two specifications, 64MB or 128MB, with parity check. The starting position is specified by the base address register 3. The parity check function needs to be enabled by setting a specific register, and write operations need to be performed at the 32-bit or 64 bit boundary.

Interrupt circuit: There is a single PCI interrupt output (INTA #), and the interrupt source can be enabled and monitored separately through multiple registers. The interrupt circuit is divided into two layers, and the second layer interrupt is transmitted to the first layer through the LINTi # signal.

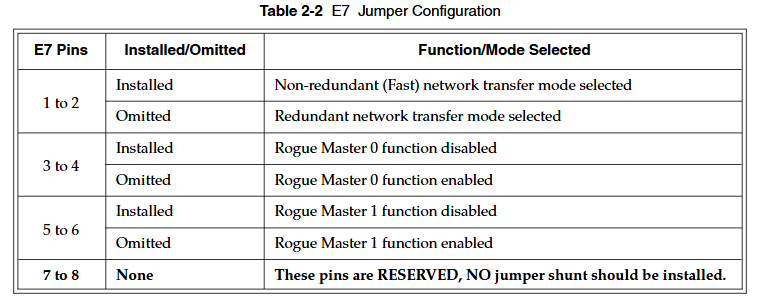

Redundant transmission mode: Removing the jumper blades between pins 1-2 of jumper E7 can configure it as redundant mode. At this time, each data packet is transmitted twice, and the receiving circuit evaluates the transmission situation. Although this mode reduces the probability of data loss, it will also lower the effective network transmission rate.

**Rogue packet removal operation * *: Rogue packets are packets that do not belong to any node in the network. VMIPCI-5565 can run as one of the two Rogue hosts to detect and remove rogue packets. After detection, relevant flags will be set and PCI interrupts can be triggered.

Configuration and Installation

Unpacking procedure: Components are sensitive to static electricity and should be handled on conductive materials. When not in use, they should be stored in their original packaging. Upon receipt, they should be inspected for any transportation damage and claims should be promptly processed.

Jumper configuration and position

The node ID is set by the 8 jumper blades of jumper block E4, and each node ID needs to be unique. Install the jumper blade so that the corresponding bit is low (0), and remove it so that it is high (1).

Jumper E7 controls three functions: 1-2 pins select non redundant or redundant network transmission mode, 3-4 pins enable or disable rogue host 0 function, 5-6 pins enable or disable rogue host 1 function, 7-8 pins are reserved pins and should not be installed with jumper blades. The default configuration is to install jumper blades on all pins except 7-8.

Physical installation: Before installation, it is necessary to ensure that the node ID and operation mode have been set. Power off the installation, firmly insert the board into the PCI connector and fix the screws, then reinstall the chassis cover and turn on the power. The board design complies with the PCI 2.2 specification.

Front panel description: There are three LED indicator lights, the red status LED is user-defined, and it is on by default when turned on. The status can be switched by writing to bit 31 of the control and status registers; The yellow signal detection LED lights up when the receiver detects light; The green self data LED lights up when it detects the return of its own data. There are also "RX" receiver ports and "TX" transmitter ports, which use "LC" type fiber optic cables. Dust caps should be installed when not connected to the cables, and eye injuries should be avoided when not powered.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba