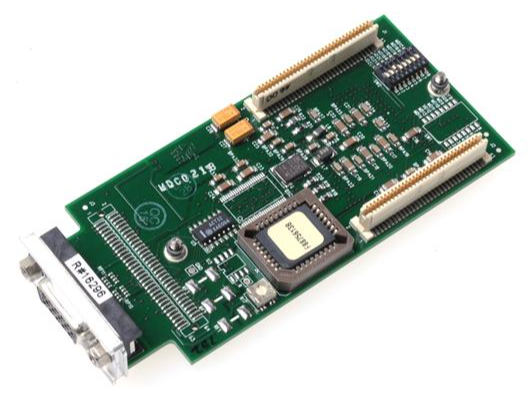

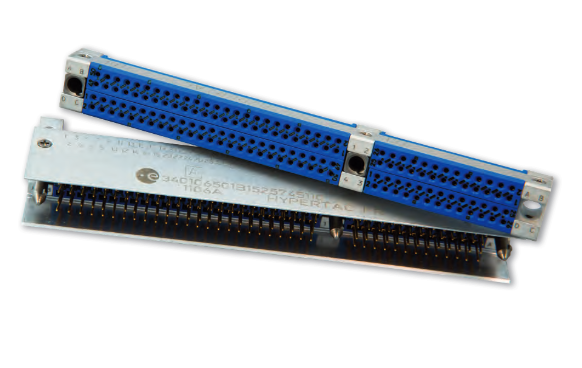

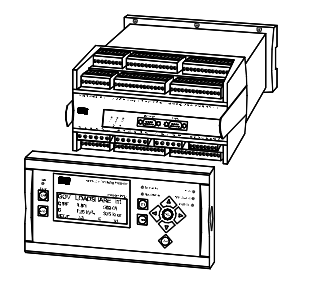

GE DS200FHVAG1A High Voltage Gate Interface Board

GE DS200FHVAG1A High Voltage Gate Interface Board

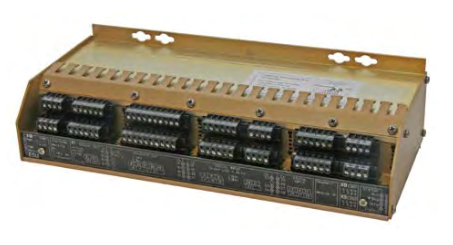

Part Number DS200FHVAG1A Manufacturer General Electric Country of Manufacture As Per GE Manufacturing Policy Series Mark V Function Module Availability In StockDS200FHVAG1A is a High Voltage Gate Interface Board manufactured by General Electric as part of gas turbine control systems. It is a special-purpose board that provides the necessary SCR gate interface and cell voltage monitoring functions for the LCI power converter.

The board dimensions are 3.25 and 5 wide and no power supplies are required. It operates in an ambient temperature environment of (32 - 122 F) plus (18 F). rise inside the cabinet. It provides an isolated path for gate power from the gate plus amplifier board to one 77mm SCR. Since the voltage drops across the SCR and sends a signal back to the FGPA. LED mounted on a board when SCR blocking voltage is present. DS200FHVAG1A Circuit Details This board includes circuitry to: Provide an isolated path for gate power from the Gate Pulse Amplifier (FGPA) board to one 77 mm SCR.

When the voltage drop across the SCR exceeds a certain threshold, send a signal back to the FGPA. When an SCR blocking voltage is present, light an LED mounted on the board. This LED is used to indicate the presence of cell voltage. Gate Pulse Transformer A toroidal current transformer (CT) soldered to the board serves as the gate pulse transformer. The single-turn primary wire from the board can be centered in the CT window thanks to a hole in the board. Because of this design, the CT can withstand the electrostatic corona that surrounds power wiring.

Gate Termination Circuit This circuit rectifies the gate transformer's output, provides enough burden resistance to ensure good noise immunity, and connects to the SCR gate leads. SCR Cell Status Circuit The FHVA board determines whether the SCR is in the OFF mode by sensing the presence of current in the 10K ohm equalizer resistor connected in parallel with the SCR. Diagnostic LED The SCR Status Circuit also illuminates a red LED labeled C STAT to indicate the presence of blocking voltage. When the bridge power is turned on, the light from this LED should be visible, though it will dim slightly as the SCR conduction angle is increased.

DS200FHVAG1A Application Data Resistor Protection If the FHVA is powered on without an SCR gate connected to P1, pins P1-1 and P1-2 should be shorted together. This keeps resistors R1 and R2 from overheating. Fiber-optic Transmitter Protection If the FHVA board is left unconnected for an hour or more, insert a rubber plug in U1 to prevent dust accumulation on the lens. DS200FHVAG1A Connections Fiber-optic transmitter U1 (Gray). The presence of voltage across SCR T1 is indicated by the output.

The primary connection is made through the T1 CT window. For best corona avoidance, center in the CT window. To SCR Gate, P1-1. Gate power is sent to the SCR gate. (The white conductor of a Red/White pair.) P1-2 to the SCR cathode SCR gate power return (The red conductor of a Red/White pair.) Connection of the equalizer resistor E1. (stab joiner) E2 -Equalizer current return path from status circuit to SCR.

OTHER INFORMATION

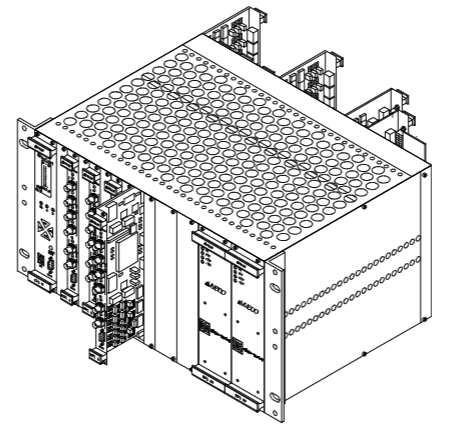

• Up to 1.26 GHz Pentium® III processor with 256 KB advanced transfer cache

• Up to 512 MB PC-133 SDRAM using a single SODIMM

• Internal AGP SVGA controller with 4 MB display cache

• 133 MHz system bus via Intel® 815E chipset

• Dual Ethernet controllers supporting 10BaseT and 100BaseTX interfaces

• Optional PCI dual channel Ultra160 SCSI

• Up to three (two with rear I/O support) PMC expansion sites (IEEE-P1386 common mezzanine card standard, 5 V)

• Up to 1 GB bootable flash on secondary IDE (optional)

• Two 16-bit and two 32-bit programmable timers

• 32 KB of nonvolatile SRAM

• Software-selectable watchdog timer with reset

• Remote Ethernet booting

• Optional IDE hard disk drive

• VME64 modes supported: A32/A24/D32/D16/D08(EO)/MBLT64/BLT32

• VMEbus interrupt handler, interrupter and system controller

• Includes real time endian conversion hardware for littleendian and big-endian data interfacing (patent no. 6,032,212)

• Enhanced bus error handling

• Passive heat sink

- User name Member Level Quantity Specification Purchase Date

- Satisfaction :

-