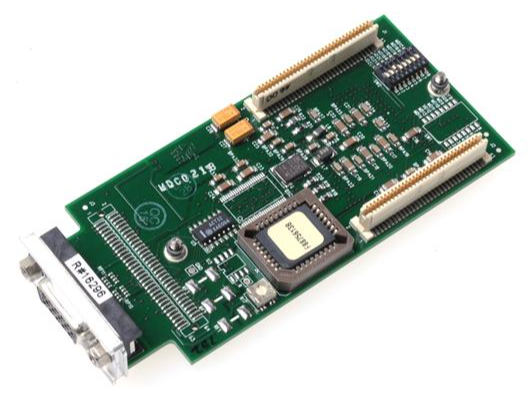

GE IS200JPDVG1A Isolated Digital Input/Output Module

GE IS200JPDVG1A Isolated Digital Input/Output Module

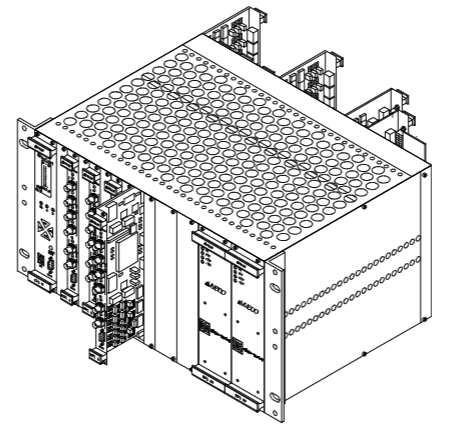

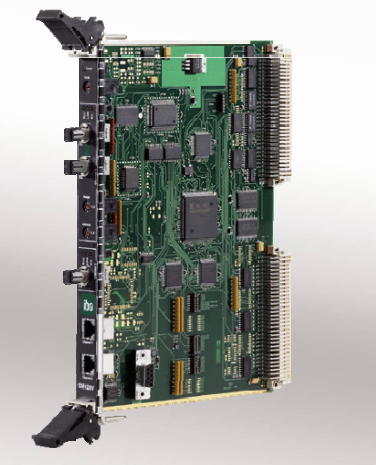

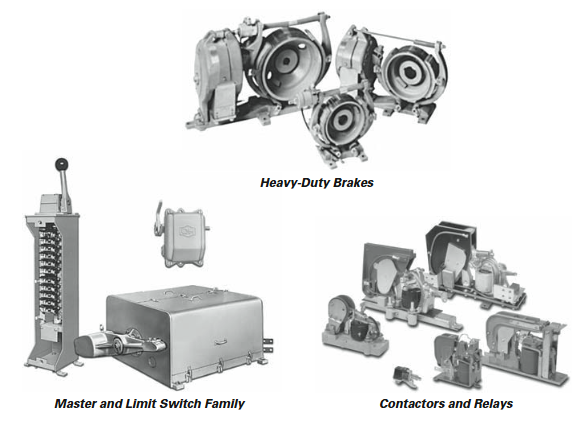

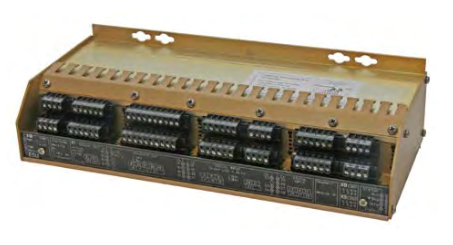

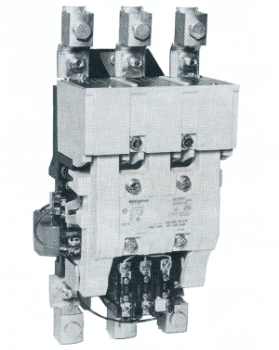

Part Number IS200JPDVG1A Manufacturer General Electric Country of Manufacture As Per GE Manufacturing Policy Series Mark VI/VIe Function Module Availability In StockThe IS200JPDVG1A developed by General Electric is a board component created by GE for their Speedtronic Mark VI system. These systems are designed for the management of heavy-duty gas and steam turbines. This board is one of many Power Distribution boards used in the Mark VI system and is built with two multi-pin female ribbon connectors located side-by-side along one long side of the board.

Each connector has a transistor placed next to it and the board has two rectangular cut-outs marked JA1 and JB1. There is also one metal oxide varistor eight other varistors and several small capacitors. Additional features include one quick-connect screw connector, one male 3-pin header connector, one 4-position plug, two 3-position plugs and five 2-position plugs. The board also has one vertical fiber-optic connector and is marked with the GE logo, the board number, and with several codes.

SPECIFICATIONS:

Part Number: IS200JPDVG1A

Manufacturer: General Electric

Series: Mark VIe

Product Type: Isolated Digital Input/Output Module

Number of channels: RS-485

Input span: 1 - 5 V dc

Outputs: 24 V dc

Generator current inputs: 0 to 5 A

Analog inputs Current inputs: 4-20 mA

Analog output current: 0-20 mA

Size: 15.9 cm high x 17.8 cm

Operating Temperature: 30 to +65°C

Frequency: 50 or 60 Hz

Repair: 3-7 Day

Availability: In Stock

Country of Origin: United States

Manual: GEH-6800_Vol_II

FUNCTIONAL DESCRIPTION:

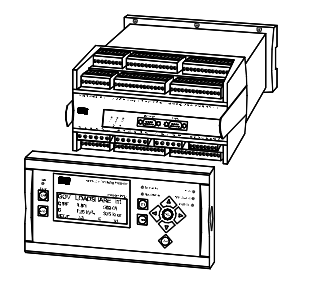

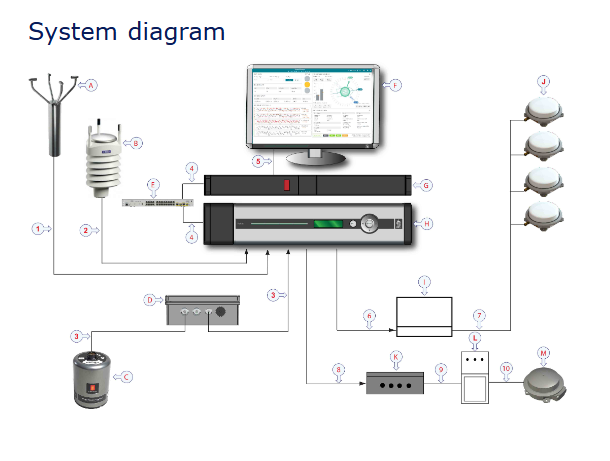

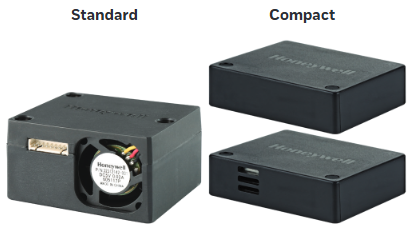

IS200JPDVG1A is an Isolated Digital Input/Output Module Manufactured and designed by General Electric as part of the Mark VIe Series used in GE Distributed Turbine Control Systems. The ARCNET I/O pack (PIOA) provides an interface for the excitation control. The I/O pack mounts to the JPDV terminal board through a 37-pin connector. The LAN connections are made to the JPDV. System input to the I/O pack is through dual RJ-45 Ethernet connectors and a 3-pin power input. Visual diagnostics are provided through indicator LEDs. Excitation control ARCNET uses a single PIOA in the core for simplex applications or a single PIOA to and cores for redundant applications.

INSTALLATION:

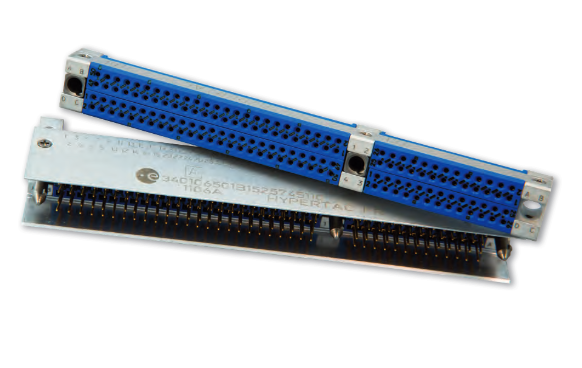

The PIOA I/O pack only mounts to the JPDV terminal board. JPDV has two DC-37 pin connectors. For an ARCNET interface to the excitation control, the PIOA mounts to the JA1 connector.

Plug the PIOA I/O pack into the JA1 terminal board connector for an ARCNET excitation control interface.

Mechanically secure the I/O pack using the threaded studs adjacent to the Ethernet ports. The studs slide into a mounting bracket specific to the terminal board type.

The bracket location should be adjusted such that there is no right-angle force applied to the DC-37 pin connector between the pack and the terminal board. The adjustment should only be required once in the life of the product.

Plug in one or two Ethernet cables depending on the system configuration. The PIOA will operate over either port. If dual connections are used, the standard practice is to connect ENET1 to the network associated with the R controller.

Apply power to the PIOA by plugging in the connector on the side of the I/O pack. It is not necessary to insert this connector with the power removed from the cable as the I/O pack has inherent soft-start capability that controls the current inrush on the power application.

OPERATION:

The I/O interface acquisition board (BIOA) has a UART to interface the processor to the RS-485 (no longer used), an ARCNET controller chip to interface the processor to the excitation control DLAN+ LAN, and a programmed complex programmable logic device (CPLD) to provide the glue logic for the hardware interfaces. The serial communication LEDs (ARx, ATx, Rx, Tx) are on the BIOA board but driven by the processor.

For more information, you can call 15305925923!

- User name Member Level Quantity Specification Purchase Date

- Satisfaction :

-