OMRON K-type PLC Maintenance Guide

OMRON K-type Programmable Controller: A Comprehensive Technical Guide from Programming Fundamentals to Troubleshooting

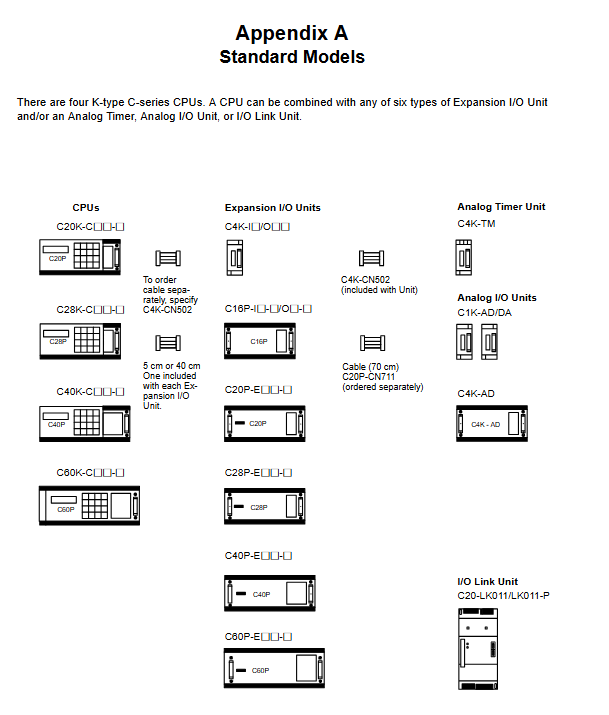

In the development process of industrial automation, the emergence of programmable controllers (PCs) has completely changed the face of relay control systems. OMRON K-type PLC (including C20K, C28K, C40K, C60K), as a representative of early compact controllers, has been widely used in small and medium-sized automation equipment due to its flexible I/O configuration, rich instruction set, and reliable ladder diagram programming method. Although modern PLCs are more powerful, a large number of K-type PLCs are still in service on production lines. This article is based on the original factory operation manual and provides a comprehensive technical guide for automation engineers and maintenance personnel, covering hardware configuration, memory structure, programming methods, instruction application, debugging skills, and troubleshooting.

Chapter 1: Product Overview and Hardware Configuration

1.1 K-type CPU series

OMRON K-type PLC offers four CPU models, with the difference being the number of I/O points:

Model Input Points Output Points Total I/O

C20K 12 8 20

C28K 16 12 28

C40K 24 16 40

C60K 32 28 60

Each CPU can be connected to expansion I/O units, analog timer units, analog I/O units, or I/O link units. The extended I/O units include models such as C4K, C16P, C20P, C28P, C40P, C60P, etc., which are connected in series on the right side of the CPU through dedicated cables. When configuring the system, it should be noted that the total number of units (2 for C40K/C60K CPU and C40K/C60K expansion units, and 1 for others) should not exceed 5, and the total length of all cables should be less than 1.2 meters.

1.2 Power and Environmental Requirements

The power supply voltage of K-type PLC is 100-240VAC (or 24VDC), the working temperature is 0-50 ℃, and the humidity is 20-85% RH (without condensation). The installation environment should avoid direct sunlight, excessive temperature/humidity, condensation, corrosive or flammable gases, dust/salt, water/oil/chemicals, shock/vibration, strong electromagnetic fields, etc. The control cabinet needs to ensure good ventilation and must be grounded (grounding resistance ≤ 100 Ω).

1.3 Front panel indicator lights

POWER: Power indicator

RUN: Lights up when CPU is running normally

ERR: Illuminates when a fatal error occurs, while RUN goes off, CPU stops, and all outputs are turned off

ALARM: Illuminates when non fatal error occurs, PC continues to run

These indicator lights are the first basis for quickly diagnosing faults on site.

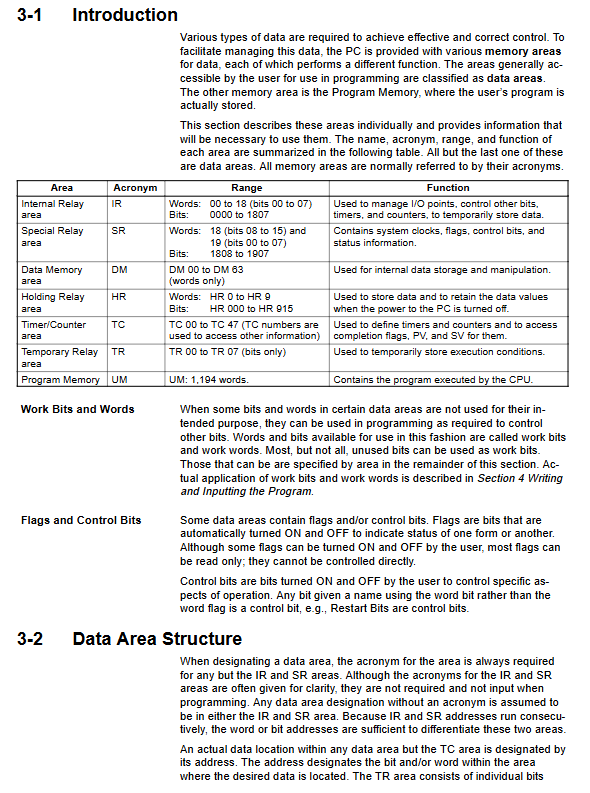

Chapter 2: Memory Structure - Fundamentals of Programming

The memory of K-type PLC is divided into multiple data areas and a program storage area (UM). Understanding these areas is a prerequisite for proper programming.

2.1 Internal Relay Area (IR)

The IR area is used to manage I/O points, control other bits, and temporarily store data. The address range is from words 00 to 18 (16 bits per word). among which

Words 00~09: allocated to I/O points (even numbers are input words, odd numbers are output words)

Words 10-18: As work bits, they can be used for internal logical operations

The allocation of I/O words varies among different CPUs: C20K only has words 00 and 01 (12 inputs/8 outputs); C28K words 00~03 (16 inputs/12 outputs); C40K characters 00~03 (24 inputs/16 outputs); C60K characters 00~03 (32 inputs/28 outputs). Unused IR positions can be used as working positions.

2.2 Special Relay Zone (SR)

The SR area contains system flags and control bits, with address range words 18-19 (bits 1804-1907). The key signs include:

Address function

1808 Battery Alarm Flag (ON when battery voltage is low)

1809 cycle time error flag (ON when ≥ 100ms)

1812 Constant OFF Logo

1813 Constant ON Logo

1815 First cycle flag (first cycle ON after program startup)

1903 instruction execution error flag (ER)

1904 carry mark (CY)

1905 is greater than the symbol (GR)

1906 equals the symbol (EQ)

1907 Less than Flag (LE)

1900~1902 0.1 seconds/0.2 seconds/1 second clock pulse

The constant ON/OFF flag can be used for conditions that require permanent connection or disconnection. Clock pulses can be used to generate timed or flashing outputs.

2.3 Data Storage Area (DM)

The DM area is a word access area (not addressable by bit), with addresses DM00~DM63, and is maintained when powered off. When using the high-speed drum counter (HDM), DM32~63 is occupied; When using the reversible drum counter (RDM), DM00~31 is occupied. The DM area is usually used to store set values, recipe data, etc.

2.4 Maintain Relay Zone (HR)

HR area letters HR0~HR9 (bits HR000~HR915), power off and hold, can be accessed by word or bit. Suitable for control that requires state retention after power outage (such as device state memory).

2.5 Timer/Counter Area (TC)

The TC area provides a total of 48 timer/counter numbers from TC00 to TC47. Each number can only be defined as a timer or counter (non repeatable). Accessing through TC number:

Completion flag (bit): ON when timing/counting arrives

Current value (PV): Word data

Set value (SV): Set through programmer

2.6 Temporary Relay Area (TR)

The TR area provides 8 bits from TR0 to TR7 for temporarily storing execution conditions at the branch points of the ladder diagram. Only used in conjunction with LD and OUT instructions, the same TR bit cannot be reused for OUT in the same instruction block, but can be used multiple times for LD.

2.7 Program Memory (UM)

UM has a capacity of 1194 words and stores user programs. The program starts at address 0000 and ends with the END (01) instruction. Each instruction occupies 1-4 words.

Chapter 3: Fundamentals of Ladder Diagram Programming

3.1 Basic Instructions

The ladder diagram consists of a left bus, a condition (normally open/normally closed), and a right output command.

Command symbol function

LD normally open contact starts the logic block in the state of pointing position

LD NOT normally closed contact starts the logic block with the reverse state of the pointing position

AND concatenates normally open and current execution condition logic and

AND NOT concatenates normally closed and current execution condition logic with non

OR parallel normally open and current execution condition logic or

OR NOT parallel normally closed and current execution condition logic OR NOT

OUT coil outputs the execution condition to the designated location

OUT NOT inverting coil will execute condition inversion and output

END (01) The program ends and must be placed at the end

3.2 Logical Block Instructions (AND LD/OR LD)

When there are complex series parallel combinations in a ladder diagram, the circuit needs to be decomposed into logic blocks and then combined with AND LD (series block) or OR LD (parallel block). For example, when two parallel branches are connected in series, start each branch separately with LD, and then combine them with AND LD. When programming, you can choose to combine the first two blocks first and then combine the subsequent blocks one by one, or list all blocks first and then combine them in reverse order using AND LD (up to 8 blocks).

3.3 Branches and Temporary Storage (TR Bit)

When there is still a serial condition in the first branch after the branch point of the ladder diagram, the execution condition after the branch point may be lost, and TR bits need to be temporarily stored. Method: Use OUT TR0 to save execution conditions at branch points, and then use LD TR0 to restore them at each branch. If there is no serial condition after the branch point (direct output), there is no need for TR bit.

3.4 Interlocking (IL/ILC) and Jumping (JMP/JME)

Interlock (IL (02)/ILC (03)): When the IL execution condition is OFF, the OUT bit between IL and ILC is forcibly OFF, the timer is reset, the counter is held, and other instructions are not executed. Suitable for situations where safe shutdown of output is required.

Jump (JMP (04)/JME (05)): Jump numbers 01~08 can only be used once. When the JMP condition is OFF, all intermediate instructions are skipped without changing any state. The jump number 00 can be used multiple times to jump to the next JME (00). Jump is suitable for situations where output status needs to be maintained (such as hydraulic and pneumatic equipment).

Chapter 4: Programmer Operation - Essential for On site Debugging

The most commonly used programming device for K-type PLCs is the Programming Console, which comes in vertical models (3G2A5-PRO13-E) and handheld models (C200H-PRO27-E).

4.1 Enter programming mode

After power on, the programmer displays "Password!". Press CLR, then press MONTR, and then press CLR to clear the display and enter. The mode switches include:

Program: Program input/modification/clearing, do not execute the program

MONITOR: Program runs to monitor and modify data

RUN: Normal execution, can only monitor

4.2 Clear Memory

Clear memory before new programming: Press CLR → Press SHIFT+CLR (MONTR display) → Press RESET (display "0000MEM CLR?") → Press MONTR. HR, TC, and DM areas can also be selectively retained.

4.3 Input Program

Taking "LD 0000" as an example:

Clear display by CLR

Enter the address (e.g. 0000) and press the down arrow key

Press the LD key, then press 0, 0, 0, 0

Press Write

Continue to input the next instruction

For function code commands (such as TIMH (15)): press FUN, enter 15, press WRITE, then enter TC number, press WRITE, enter SV, press WRITE.

4.4 Inspection Procedure

Press CLR → SRCH → SRCH, and the program will automatically check for syntax errors. If an error is found, it will stop and display an error code, press SRCH to continue. Common errors:

NO END INST: Missing END instruction

CIRCUIT ERR: Number of logical blocks does not match

COIL DUPL: The same output bit is controlled by multiple instructions

IL ILC ERR: IL/ILC mismatch

4.5 Surveillance and Enforcement

Bit/word monitoring: Enter the address to be monitored and press MONTR. Up to 6 addresses can be monitored simultaneously (3 displayed). In MONITOR/RUN mode, ON/OFF status will be displayed.

Force Set/Reset: In monitoring mode, press PLAY/SET to force ON and REC/RESET to force OFF (for only one scan cycle).

Modify PV/SV: While in monitoring mode, press CHG, enter the new value, and press WRITE.

4.6 Tape Drive Backup

The program can be saved/restored by connecting to a standard cassette recorder through the MIC and EAR interfaces of the programmer. Operation steps: Press EXT, enter the file number (00~99), start the recorder, and within 5 seconds, press SHIFT+REC/RESET (save) or SHIFT+PLAY/SET (restore) or VER (compare).

Chapter 5: Detailed Explanation of Instruction Set (Selected)

The K-type PLC has a rich instruction set, and the following are the most commonly used types.

5.1 Timer and Counter

TIM: 100ms countdown timer, SV range 000.0~999.9 seconds (input with decimal point removed, e.g. # 0150 represents 15.0 seconds). Start timing when the execution condition is ON and reset when it is OFF. Complete the flag ON when reaching SV.

TIMH (15): 10ms high-speed timer, SV range 00.02~99.99 seconds (e.g. # 0500 represents 5.00 seconds). Note that a cycle time>10ms will affect accuracy.

CNT: Countdown counter, SV range 0~9999. When the rising edge of the CP pulse is reduced by 1 and the R reset input is ON, PV is reset to SV. When it reaches 0, the flag ON is completed.

CNTR (12): Reversible circular counter. The rising edges of II (increase count) and DI (decrease count) respectively increase or decrease PV. When decreasing from 0 to 0, it becomes SV, and when increasing from SV to SV, it becomes 0, while completing the flag ON.

5.2 Differential Instructions

DIFU (13): Rising edge differentiation. When the execution condition changes from OFF to ON, the designated bit is ON for one scan cycle.

DIFD (14): Falling edge differentiation. When executing the condition ON → OFF, specify the bit ON for one cycle.

5.3 Maintain Instructions

KEEP (11): Similar to a latch relay. Set when S input is ON, reset when R input is ON. Even in the interlocking zone, the state remains unchanged.

5.4 Shift instruction

SFT (10): Shift bit register. I (input bit), P (rising edge of shift pulse), R (reset). Move the state of I to the lowest bit specified by St, shift to the left, and lose the highest bit.

SFTR (84): Reversible Shift Register. Control bit 15 (reset), bit 14 (allow shift), bit 13 (input), and bit 12 (direction) of control word (C).

WSFT (16): Word shift. Move the St character content to St+1, St+1 to St+2,..., the E character content is lost, and the St character is reset to zero.

5.5 Data Transmission

MOV (21): Transfer the source word (or constant) to the target word.

MVN (22): Reverse the source word and transmit it.

5.6 Comparison Instructions

CMP (20): Comparing Cp1 and Cp2, the results affect the GR (greater than), EQ (equal to), and LE (less than) flags. Attention: The logo will be changed by subsequent instructions and must be used immediately.

5.7 Arithmetic Operations (BCD)

ADD (30): Au+Ad+CY → R, CY is rounded up.

SUB (31): Mi Su CY → R, when the result is negative, CY=1 and R is the complement of 10.

MUL (32): Md × Mr → R (low 4 bits) and R+1 (high 4 bits).

DIV (33): Dd ÷ Dr → R (quotient), R+1 (remainder).

STC (40): Set carry flag; CLC (41): Clear carry flag.

5.8 Special Instructions

HDM (61): High speed drum counter. Using input 0000 as the 2kHz counting input, compare the current value with the 16 preset upper and lower limits in DM32~63, and store the result in the 16 bits of the specified result word. Reset can be done with either a hard reset (input 0001) or a soft reset (SR1810).

RDM (60): Reversible drum counter. Use SR1804 (reset), 1805 (count), 1806 (direction), store the current value in TC46, and compare it with the 16 preset upper and lower limits in DM00~31.

IORF (97): Immediately refresh the specified range of I/O words for situations that require fast response.

ENDW (62): Set the minimum cycle time in units of 100 μ s × M.

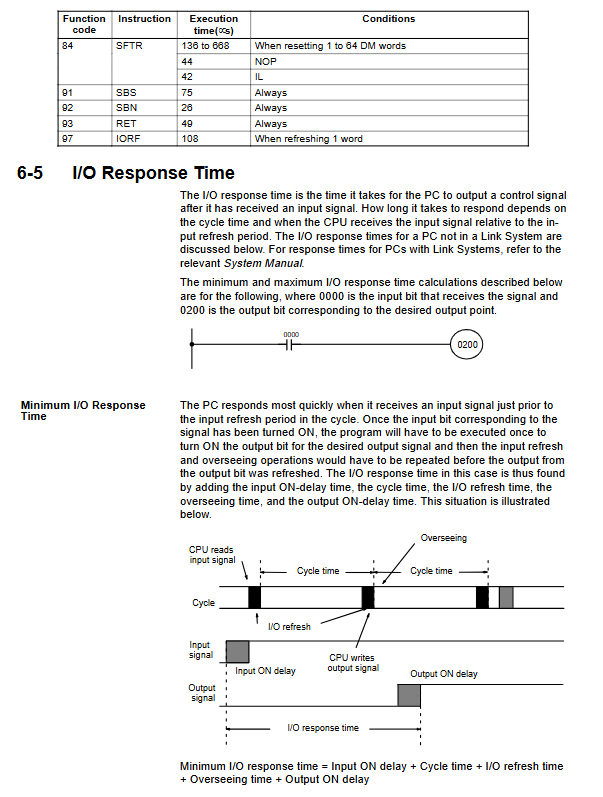

Chapter 6: Loop Time and I/O Response Time

6.1 Composition of cycle time

The CPU executes sequentially in each cycle:

Monitoring (1.6ms fixed): watchdog timer refresh, memory check

I/O refresh (0.51ms+0.03ms x (I/O word count -2)): read input, write output

Peripheral service: Processing programmer commands, time=(monitoring+refresh+instruction execution) × 0.05, rounded off as 1ms if less than 1ms, rounded off as 0.5ms if more than 1ms

Instruction execution: the sum of the execution time of each instruction

When the cycle time exceeds 100ms, SR1809 is turned on and the ALARM light is on; When it exceeds 130ms, the ERROR light will turn on and the CPU will stop.

6.2 Example of Instruction Execution Time

LD/IND/OR: approximately 11.5-12 μ s

OUT(ON):17μs; OUT(OFF):17.5μs

TIM (Timing): 95 μ s; TIM (reset): 95.5-186.5 μ s

MOV (Constant to Word): 109 μ s

CMP (Constant to Word): 121.5 μ s

ADD:233μs

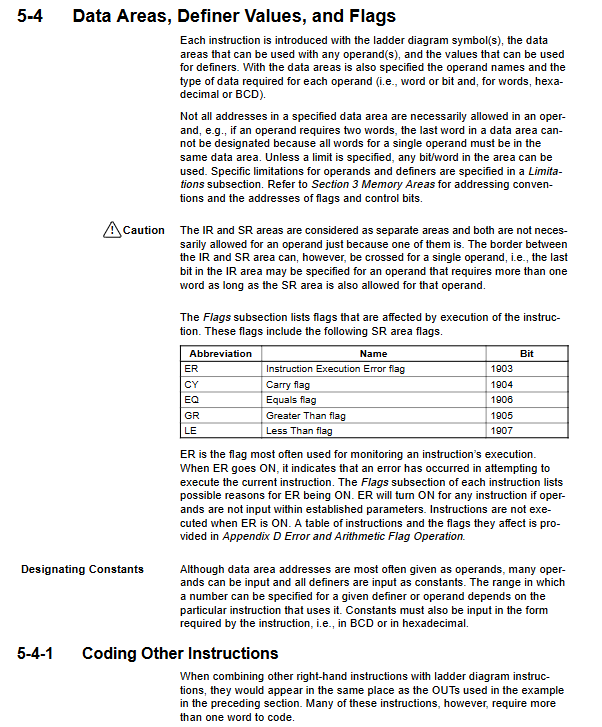

6.3 I/O response time

Minimum response time=input ON delay+cycle time+I/O refresh time+monitoring time+output ON delay. Maximum response time=input ON delay+2 x cycle time+monitoring time+output ON delay (when the input arrives just after I/O refresh).

Chapter 7: Fault Diagnosis and Common Errors

7.1 CPU indicator light malfunction

Possible causes and solutions for the phenomenon

POWER is not on and there is no power supply. Check the power supply

RUN does not light up, ERR lights up fatal errors (memory error, no END, I/O bus error, etc.) Switch to Program mode, check the program, clear the error

ALARM light cycle time exceeds 100ms or battery low check program efficiency, replace battery

RUN/ERR/ALARM do not light up. CPU hardware failure. Replace CPU

7.2 Programmer Error Messages

Message meaning processing

NO END INST program does not have END (01) written at the end

CIRCUIT ERR Check if AND LD/OR LD is used correctly for instruction quantity mismatch in logical blocks

COIL DUPL is controlled by multiple instructions to check if OUT, KEEP, DIFU, etc. reuse the same address for the same output bit

IL-ILC ERR IL/ILC unpaired ensures that each IL has a corresponding ILC

JMP-JME ERR JMP/JME unpaired check jump number

The subroutine called by SBN UNDEFD does not exist to check the subroutine number of the SBS call

STEP OVER: If there are more than 16 steps, reduce the number of step segments

***PROG OVER program exceeds memory capacity, removes redundant instructions or uses larger memory units

***ADDR OVER Address Out of Range Check operand address

7.3 Special marker diagnosis

SR1808 (battery alarm): The battery voltage is low and needs to be replaced as soon as possible (model 3G2A9-BAT08).

SR1809 (cycle time exceeding 100ms): Optimize the program or extend the watchdog time.

SR1903 (ER flag): Arithmetic operand not BCD, BCD conversion out of range, instruction operand error, etc.

7.4 Common operational troubleshooting

Fault phenomenon inspection point handling

Is the output bit of the motor not rotating (no output at the output point) driven by the program; Output unit power supply; Fuse inspection ladder diagram; Check the power supply of the output unit

Input signal does not respond to input bit status monitoring; Input unit wiring; Check the external switch of the input public terminal; Check input unit model matching

Is the timer not working? Is the TIM execution condition ON? Is SV 0; Whether to adjust the program in the interlocking area; Check IL conditions

Does the counter count whether the CP pulse is valid; Is R always ON to check the CP edge; Check the reset logic

Analog input unit settings for abnormal analog values; Range of measurement; Wiring inspection DIP switch; Check the signal source

Communication failure (link unit) unit number setting; Cable; Station number verification system manual

Chapter 8: Maintenance and Preventive Measures

8.1 Regular inspection items

Environment: temperature, humidity, dust, corrosive gases

Electrical: Input voltage (100~240VAC or 24VDC), grounding resistance

Connection: Terminal screws are tightened, cables are undamaged, connectors are locked tightly

Battery: Replace every 1-2 years or immediately when SR1808 is turned on. Before replacing the battery, ensure that the PLC is powered on (otherwise the program may be lost), and then turn off the power before turning it back on.

Heat dissipation: Remove dust from ventilation holes

8.2 Program Backup

It is strongly recommended to save a copy of the program through a tape drive or EPROM writer after debugging is completed. The EPROM writer (C500-PRW06) can write programs to 2764 EPROM and then install them on the CPU for permanent storage.

8.3 Precautions for CPU Replacement

When replacing the CPU, it is necessary to read and write the DM and HR data (such as recipe and current counter values) of the original CPU into the new CPU through a programmer, otherwise it may cause abnormal operation. The entire program and data can be restored using a tape drive.

8.4 Safety precautions

It is strictly prohibited to disassemble units, terminals, or cables while they are powered on.

After power failure, wait for at least 1 minute (discharge of large capacitor), confirm that the POWER light is off, and then touch the interior.

Before conducting a voltage withstand test, the functional grounding terminal must be disconnected.

External hard wired safety measures such as emergency stop circuits and limit switches must be provided, and cannot rely solely on PLC programs.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba