OMRON CP1H PLC Practical Manual

The I/O memory of CP1H adopts a similar architecture to CS/CJ series, but the I/O allocation method is the same as CPM series (fixed area).

3.1 CIO Area (Core I/O Area)

Built in input: CIO 0.00~CIO 1.11 (24 o'clock)

Built in output: CIO 100.00~CIO 101.07 (16 points)

Expansion unit input: Allocate sequentially starting from CIO 2

Expansion unit output: allocated sequentially starting from CIO 102

Data link area: CIO 1000~1199

CPU bus unit area: CIO 1500~1899

Special I/O Unit Area: CIO 2000~2959

Serial PLC link area: CIO 3100~3189

DeviceNet area: CIO 3200~3799

Internal workspace: CIO 1200~1499, CIO 3800~6143

3.2 Work Area (W)

W0~W511 (512 characters), pure internal working bit, power off reset (IOM hold bit can be held)

3.3 Holding Zone (H)

H0~H511 (512 characters), power off hold, suitable for devices that require memory states

3.4 Auxiliary Area (A)

A0~A447: Read only system flag

A448~A959: Read and write (such as A500.12 IOM hold bit, A500.15 output OFF bit, etc.)

3.5 Timer/Counter Area

T0~T4095 (4096 timers), C0~C4095 (4096 counters)

You can choose BCD mode (0~9999) or binary mode (0~65535)

3.6 Data Storage Area (D)

D0~D32767 (32K characters), keep powered off

D20000~D29599: Used for CJ series special I/O units

D30000~D31599: Used for CJ series CPU bus units

D32200~D32299 (serial port 1)/D32300~D32399 (serial port 2): Modbus RTU for easy main station use

3.7 Index registers (IR0~IR15) and data registers (DR0~DR15)

Used for indirect addressing, supporting automatic addition, subtraction, offset and other operations

By default, each task is independent and can be set as shared in CX Programmer

Chapter 4: Core Built in Functions - High speed Counting and Pulse Output

4.1 High speed counter (up to 100kHz/1MHz)

CP1H has 4 built-in high-speed counters (Y-shaped with 2 dedicated 1MHz terminals). Set up through PLC Setup:

Input modes: differential phase (4th harmonic), pulse+direction, increasing/decreasing pulse, single-phase increasing

Counting mode: linear mode (range -2147483648~+2147483647) or circular mode (0~set maximum value)

Reset methods: Z-phase+software reset, software only reset, Z-phase with comparison continuation+software reset, etc

Comparison function: Target value comparison (up to 48 points) or region comparison (up to 8 intervals), triggering interrupt tasks when PV matching (0~255)

Use the CTBL (882) instruction to register the comparison table, the INI (880) instruction to control the start and stop of the comparison, and the PRV (881) instruction to read PV or frequency. Frequency measurement only supports counter 0.

4.2 Pulse output (positioning and speed control)

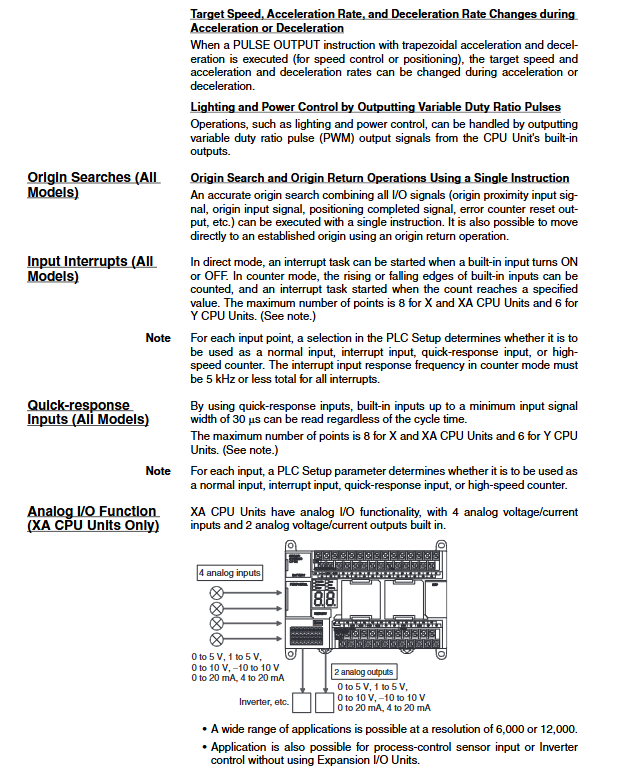

Built in 4-channel pulse output (Y-shaped with 2-channel 1MHz line driven output). The output mode can be CW/CCW or pulse+direction.

SPED (885): No acceleration/deceleration pulse output (continuous or independent mode)

ACC (888): with acceleration/deceleration pulse output (acceleration rate=deceleration rate)

PLS2 (887): with acceleration/deceleration pulse output (acceleration rate ≠ deceleration rate, supports starting frequency)

PULS (886): Set the number of pulses (used in conjunction with SPED or ACC)

ORG (889): Origin Search/Origin Return

INI (880): Stop pulse output or change PV

PWM (891): Variable duty cycle pulse output (frequency 0.1~6553.5Hz, duty cycle 0.0~100.0%)

Key features:

Multi stage startup: PLS2 can be executed again during execution to change the target position, speed, and acceleration/deceleration rate

Triangle control: When the required number of pulses for acceleration and deceleration exceeds the total number of pulses, the constant speed segment is automatically cancelled

Automatic selection of absolute coordinates: After the origin is determined, CW/CCW is automatically selected based on the current PV and target values

Interrupted feed: In speed control (continuous mode), executing PLS2 can switch to positioning mode and stop after outputting a fixed pulse

4.3 Origin Search and Origin Return

To execute through ORG (889), it is necessary to enable and set parameters in the PLC Setup:

Operation modes: 0 (no deviation counter reset, no positioning completion input), 1 (deviation counter reset), 2 (positioning completion input)

Search direction: CW or CCW

Detection method: Select the inversion method based on the near origin signal

Speed parameters: starting speed, high speed, approach speed, acceleration and deceleration rate

Origin compensation: offset by a specified number of pulses after detecting the origin

Limit input: CW/CCW limit switch type (normally open/normally closed)

During the origin search process, the external limit switch signal needs to be written into A540.008-A543.09 (CW limit mark) and A540.009-A543.09 (CCW limit mark). The origin search error code is stored in A444/A445, etc.

Chapter 5: Interrupt Function - Real time Response

5.1 Input Interrupt (Direct Mode)

X/XA type: 8 points (CIO 0.00~0.03, CIO 1.00~1.03)

Y-shaped: 6 points (CIO 0.00~0.01, CIO 1.00~1.03)

Triggered by rising or falling edge, with a response time of approximately 0.3ms

Corresponding interrupt tasks 140~147

5.2 Input Interrupt (Counting Mode)

The same terminal can be set to counter mode, triggering an interrupt when the count reaches the set value

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba