OMRON K-type PLC Maintenance Guide

The program can be saved/restored by connecting to a standard cassette recorder through the MIC and EAR interfaces of the programmer. Operation steps: Press EXT, enter the file number (00~99), start the recorder, and within 5 seconds, press SHIFT+REC/RESET (save) or SHIFT+PLAY/SET (restore) or VER (compare).

Chapter 5: Detailed Explanation of Instruction Set (Selected)

The K-type PLC has a rich instruction set, and the following are the most commonly used types.

5.1 Timer and Counter

TIM: 100ms countdown timer, SV range 000.0~999.9 seconds (input with decimal point removed, e.g. # 0150 represents 15.0 seconds). Start timing when the execution condition is ON and reset when it is OFF. Complete the flag ON when reaching SV.

TIMH (15): 10ms high-speed timer, SV range 00.02~99.99 seconds (e.g. # 0500 represents 5.00 seconds). Note that a cycle time>10ms will affect accuracy.

CNT: Countdown counter, SV range 0~9999. When the rising edge of the CP pulse is reduced by 1 and the R reset input is ON, PV is reset to SV. When it reaches 0, the flag ON is completed.

CNTR (12): Reversible circular counter. The rising edges of II (increase count) and DI (decrease count) respectively increase or decrease PV. When decreasing from 0 to 0, it becomes SV, and when increasing from SV to SV, it becomes 0, while completing the flag ON.

5.2 Differential Instructions

DIFU (13): Rising edge differentiation. When the execution condition changes from OFF to ON, the designated bit is ON for one scan cycle.

DIFD (14): Falling edge differentiation. When executing the condition ON → OFF, specify the bit ON for one cycle.

5.3 Maintain Instructions

KEEP (11): Similar to a latch relay. Set when S input is ON, reset when R input is ON. Even in the interlocking zone, the state remains unchanged.

5.4 Shift instruction

SFT (10): Shift bit register. I (input bit), P (rising edge of shift pulse), R (reset). Move the state of I to the lowest bit specified by St, shift to the left, and lose the highest bit.

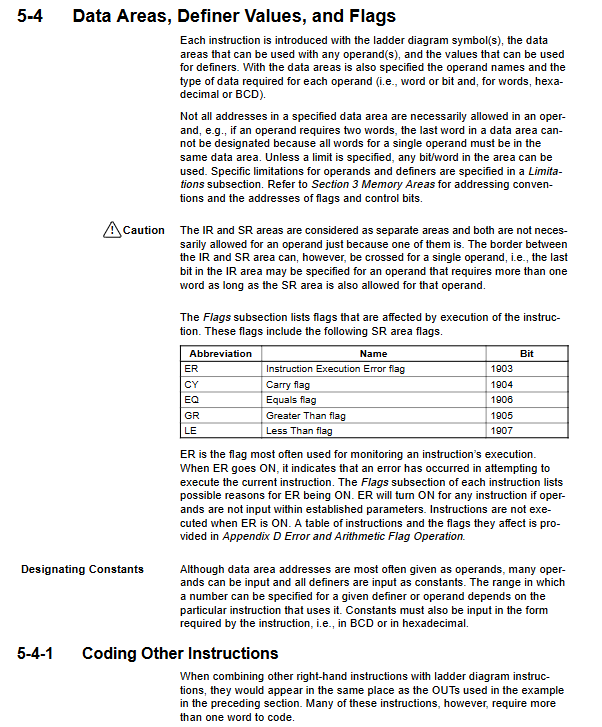

SFTR (84): Reversible Shift Register. Control bit 15 (reset), bit 14 (allow shift), bit 13 (input), and bit 12 (direction) of control word (C).

WSFT (16): Word shift. Move the St character content to St+1, St+1 to St+2,..., the E character content is lost, and the St character is reset to zero.

5.5 Data Transmission

MOV (21): Transfer the source word (or constant) to the target word.

MVN (22): Reverse the source word and transmit it.

5.6 Comparison Instructions

CMP (20): Comparing Cp1 and Cp2, the results affect the GR (greater than), EQ (equal to), and LE (less than) flags. Attention: The logo will be changed by subsequent instructions and must be used immediately.

5.7 Arithmetic Operations (BCD)

ADD (30): Au+Ad+CY → R, CY is rounded up.

SUB (31): Mi Su CY → R, when the result is negative, CY=1 and R is the complement of 10.

MUL (32): Md × Mr → R (low 4 bits) and R+1 (high 4 bits).

DIV (33): Dd ÷ Dr → R (quotient), R+1 (remainder).

STC (40): Set carry flag; CLC (41): Clear carry flag.

5.8 Special Instructions

HDM (61): High speed drum counter. Using input 0000 as the 2kHz counting input, compare the current value with the 16 preset upper and lower limits in DM32~63, and store the result in the 16 bits of the specified result word. Reset can be done with either a hard reset (input 0001) or a soft reset (SR1810).

RDM (60): Reversible drum counter. Use SR1804 (reset), 1805 (count), 1806 (direction), store the current value in TC46, and compare it with the 16 preset upper and lower limits in DM00~31.

IORF (97): Immediately refresh the specified range of I/O words for situations that require fast response.

ENDW (62): Set the minimum cycle time in units of 100 μ s × M.

Chapter 6: Loop Time and I/O Response Time

6.1 Composition of cycle time

The CPU executes sequentially in each cycle:

Monitoring (1.6ms fixed): watchdog timer refresh, memory check

I/O refresh (0.51ms+0.03ms x (I/O word count -2)): read input, write output

Peripheral service: Processing programmer commands, time=(monitoring+refresh+instruction execution) × 0.05, rounded off as 1ms if less than 1ms, rounded off as 0.5ms if more than 1ms

Instruction execution: the sum of the execution time of each instruction

When the cycle time exceeds 100ms, SR1809 is turned on and the ALARM light is on; When it exceeds 130ms, the ERROR light will turn on and the CPU will stop.

6.2 Example of Instruction Execution Time

LD/IND/OR: approximately 11.5-12 μ s

OUT(ON):17μs; OUT(OFF):17.5μs

TIM (Timing): 95 μ s; TIM (reset): 95.5-186.5 μ s

MOV (Constant to Word): 109 μ s

CMP (Constant to Word): 121.5 μ s

ADD:233μs

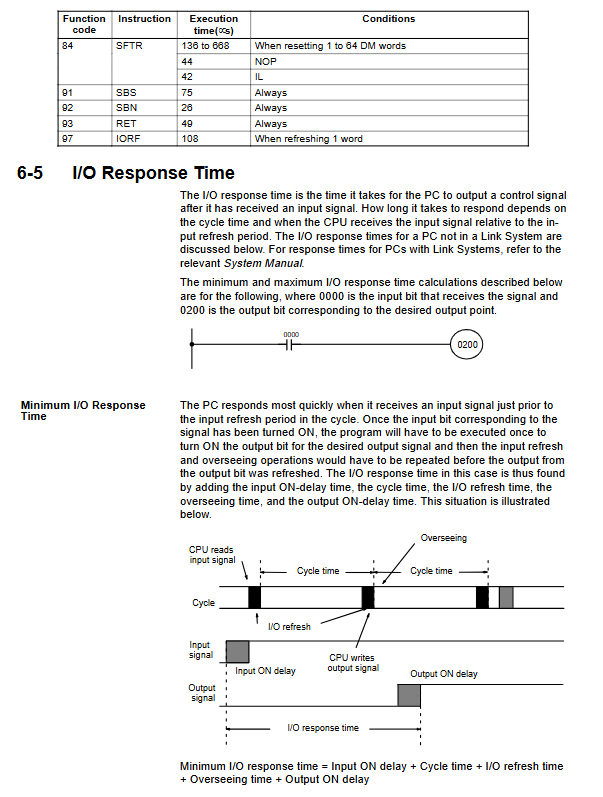

6.3 I/O response time

Minimum response time=input ON delay+cycle time+I/O refresh time+monitoring time+output ON delay. Maximum response time=input ON delay+2 x cycle time+monitoring time+output ON delay (when the input arrives just after I/O refresh).

Chapter 7: Fault Diagnosis and Common Errors

7.1 CPU indicator light malfunction

Possible causes and solutions for the phenomenon

POWER is not on and there is no power supply. Check the power supply

RUN does not light up, ERR lights up fatal errors (memory error, no END, I/O bus error, etc.) Switch to Program mode, check the program, clear the error

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba