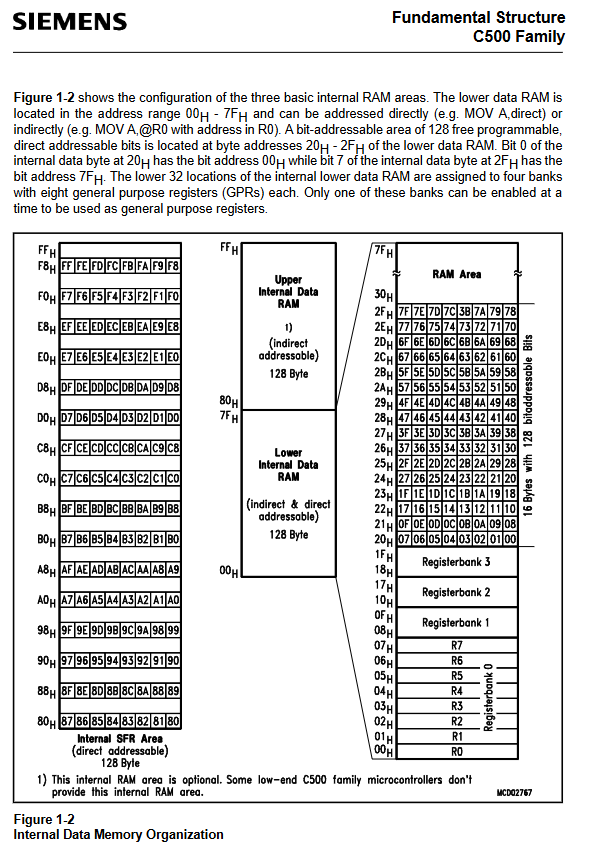

SIEMENS C500 microcontroller architecture and instruction set

CPU core enhancement: breaking through the bottleneck of single data pointer

One of the most significant architectural improvements in the C500 series is the extension of Data Pointer (DPTR). The standard 8051 only has one 16 bit DPTR for accessing external data storage or external I/O. In applications that require frequent switching between multiple memory regions or peripheral addresses, software must repeatedly perform PUSH/POP operations to save and restore DPTR, which not only consumes additional instruction cycles but also occupies valuable internal RAM stack space.

1. Implementation mechanism of eight data pointers

C500 cleverly implements up to 8 16 bit data pointers (DPTR0 to DPTR7) while maintaining full compatibility with the 8051 instruction set. Its core is an SFR called DPSEL (Data Pointer Select Register, address 92H), whose lower 3 bits (DPSEL. 2-DPSEL. 0) are used to select the currently activated DPTR. From a software perspective, any instruction to operate DPTR (such as MOV DPTR, # data16, MOVX A, @ DPTR, INC DPTR, etc.) only acts on the DPTR pointer currently selected by DPSEL. Switching data pointers only requires one instruction (such as MOV DPSEL, # 06H selecting DPTR6), without the need to use multiple instructions to save and restore pointer values like standard 8051.

2. Analysis of Performance Improvement Examples

To visually demonstrate the advantages of multiple data pointers, consider a typical table lookup transfer task: transfer a data table with a starting address of 1FFF H from the code memory (ROM) to a buffer with a starting address of 2FA0 H in the external data memory.

Using a single data pointer (such as standard C501): Each time a byte is moved, the source pointer and destination pointer need to be saved separately to the "shadow variables" in the internal RAM. For every byte moved, it takes approximately 28 machine cycles and consumes 4 bytes of RAM as shadow variables.

Use dual data pointers (such as C509): During initialization, store the source pointer in DPTR6 and the destination pointer in DPTR7. In each loop, only one MOV DPSEL instruction # 06H is needed to switch to the source pointer, read bytes, and then another MOV DPSEL instruction # 07H switches to the destination pointer for writing. It only takes about 12 machine cycles to move one byte, and there is no need for additional shadow variables.

According to the performance data provided in the manual, using multiple data pointers in the same table transfer task can reduce the execution time by half (from 28 cycles to approximately 12-14 cycles), while freeing up internal RAM space. When all 8 pointers are used simultaneously, a maximum of 24 bytes of RAM can be released for the application (16 bytes for storing pointer variables and 8 bytes for avoiding stack operations). This feature is particularly important for large-scale projects using high-level programming languages such as C51 and PLM51, as their code generation efficiency is relatively low and they tend to frequently use pointers.

3. Enhanced Hooks simulation concept

The C500 family has also introduced innovative Enhanced Hooks simulation technology. Traditionally, simulating on-chip ROM type MCUs requires expensive "bond out" chips (i.e. special versions that lead out the internal bus). The C500 integrates dedicated simulation logic inside each mass-produced chip. With the external EH-IC (Enhanced Hooks Interface Chip), the mass-produced chip itself can achieve full functional simulation, including single step execution, reading SFR after breakpoints, and simulation of all ROM/ROMless modes. This ensures that the simulated chip is identical to the mass-produced chip, eliminating behavioral differences introduced by using different wafer batches, while reducing the cost of in circuit simulators (ICE).

Interrupt system: precise guarantee of real-time response

Interrupt latency is a key indicator in real-time control systems. The interrupt handling mechanism of C500 has strict temporal determinism, allowing engineers to accurately calculate the worst-case response time.

1. Interrupt Vector and Hardware Response Process

Each interrupt source has a fixed interrupt vector address located at the low end of the code storage area. The vector address interval is 8 bytes (such as 0003H, 000BH, 0013H, etc.), and usually a jump instruction is placed here to point to the real service program. When an interrupt is accepted by the CPU, the hardware will automatically perform the following operations:

Complete the execution of the current instruction.

Push the current value of the program counter (PC) onto the stack (16 bits, low byte first).

Load the entry address (vector address) of the interrupt service program into the PC.

The program jumps to interrupt service program execution.

Important note: Not all interrupt hardware will automatically clear the interrupt request flag. Partial interrupt sources require users to clear the flag through software in the service program, otherwise the interrupt will be triggered repeatedly.

2. Blocking conditions for interrupt response

The generation of hardware LCALL (long call) will be blocked by any of the following three conditions:

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba