SIEMENS C500 microcontroller architecture and instruction set

Condition 1 (Priority Blocking): Currently processing an interrupt of the same or higher priority.

Condition 2 (instruction completion blocking): The current instruction has not yet been executed to the last machine cycle. This ensures that the current instruction can be fully executed.

Condition 3 (Critical Instruction Blocking): The currently executing instruction is RETI (Interrupt Return), or an instruction that writes to the Interrupt Allow Register (IE) or Interrupt Priority Register (IP). The blocking will continue until the instruction is executed and another instruction is executed. This mechanism ensures that modifications to the interrupt system can take effect stably.

3. Precise calculation of interrupt response time

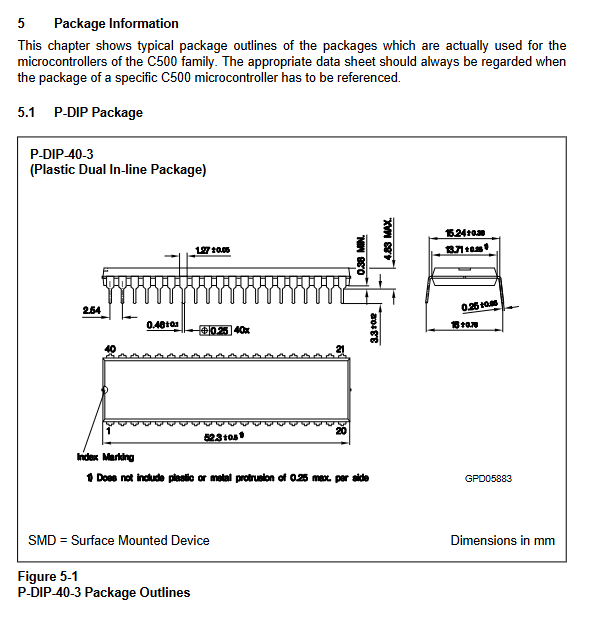

The interrupt response time is defined as the time interval between the time when the external interrupt request signal takes effect (the request flag is set) and the time when the first instruction of the interrupt service program starts executing.

According to the timing analysis in the manual, an interrupt requires at least 3 complete machine cycles from being detected to completing hardware LCALL (1 cycle for detecting flags and 2 cycles for executing LCALL). In the worst-case scenario, if the interrupt request encounters a blocking condition, the response time will be extended:

If blocked by condition 2 (instruction not completed), the maximum waiting time shall not exceed 3 cycles. Because the longest instruction (MUL or DIV) only requires 4 cycles, and interrupt detection occurs in the last cycle of each instruction.

If blocked by condition 3 (RETI or write IE/IP), the maximum waiting time should not exceed 5 cycles (1 cycle to complete the current RETI/write operation, plus up to 4 cycles to complete the immediately following instruction - if that instruction happens to be MUL or DIV).

Therefore, for a single interrupt system, the interrupt response time of C500 is always between 3 and 9 machine cycles. For a 12MHz crystal oscillator system (one machine cycle=1 µ s), this corresponds to a delay of 3 µ s to 9 µ s, providing highly predictable performance for hard real-time applications.

External Memory Access Timing and Bus Design

C500 accesses external program memory and data memory through standard bus interfaces, and understanding its timing is crucial for hardware design.

1. Address/data reuse

When accessing external memory, the P0 port assumes the time division multiplexing function for the low 8-bit address and 8-bit data, while the P2 port outputs the high 8-bit address (for MOVX @ DPTR or external fetch) or maintains its SFR content (for MOVX @ Ri). External address latches (such as 74HC373) use the falling edge of the ALE (Address Latch Enable) signal to latch the lower 8 bits of the address on port P0. Afterwards, the P0 port is switched to the data bus.

2. Two access modes

16 bit address access (MOVX @ DPTR): P2 port continuously outputs the content of DPH (high 8-bit address) throughout the entire access cycle. P0 port outputs DPL when ALE is valid, and then switches to data signal. This mode can access a complete address space of 64 KB.

8-bit address access (MOVX @ Ri): The P2 port maintains its existing SFR value throughout the entire cycle and does not automatically output the higher 8 bits of the address. The CPU uses the P0 port to output the content of Ri (8-bit address) and multiplex it with the data. This method is commonly used for "paging" expansion, where the P2 port is pre-set as a page address by software to enable external RAM access exceeding 256 bytes.

Important hardware precautions: During external memory access, the CPU will write FF H to the P0 port latch (SFR). Therefore, during external memory access, the software must not execute the MOV P0 instruction to modify the P0 port, otherwise it will damage the current bus cycle data. In addition, for the ROM free version (EA grounded), the entire 64 KB program space is external, and the P2 port will be fully occupied as an address line, which cannot be used for general-purpose I/O.

Instruction set: Functional classification and optimization of 111 instructions

The instruction set of C500 is fully compatible with the standard 8051, with a total of 111 instructions, including 49 single byte instructions (44%), 45 double byte instructions (41%), and 17 three byte instructions (15%). Efficient instruction encoding means that C500 can achieve higher code density at the same clock frequency.

Overview of Addressing Modes

C500 supports 5 addressing modes, each corresponding to a specific memory space, as shown in Table 2.

Table 2 Addressing Modes and Corresponding Memory Spaces

Memory space accessed in addressing mode

Address the R0-R7, ACC, B, CY bits of the currently selected register group DPTR

Directly addressing the low 128 bytes of internal RAM SFR

Immediate addressing of program memory (constant)

Register indirect addressing internal RAM (@ R0/@ R1/SP), external data storage (@ R0/@ R1/@ DPTR)

Base address register plus index addressing program memory (@ A+DPTR, @ A+PC), used for lookup tables

2. PSW impact of arithmetic operation instructions

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba