SBS Technologies VIPC616 Carrier Board

SBS Technologies VME System Expansion Tool: VIPC616 Industry Pack Carrier Board

In the VME bus system, the flexible expansion capability of the I/O module determines the adaptability and lifecycle of the system. VIPC616 is a mature 6U VMEbus Industry Pack carrier board that provides installation capabilities for four single width or up to two double width Industry Pack modules, supporting I/O, ID, memory, and interrupt cycles. This article will deeply analyze the design essence and usage points of VIPC616 from multiple dimensions, including application background, hardware characteristics, address mapping, interrupt management, front-end and back-end I/O allocation, power filtering and protection, environmental adaptability, supporting engineering kits, and related products.

The role of the Industry Pack ecosystem and VIPC616

Industry Pack (IP) is a modular I/O standard widely used in industrial control, data acquisition, communication, and military embedded computing. The IP module is compact and interchangeable, and can be connected to various system buses (such as VME, PCI, CompactPCI, etc.) through a carrier board. VIPC616 is precisely such a 6U VME carrier board, which converts the signal of the VME backplane into the timing and power required by the Industry Pack, while providing mechanical fixation.

Compared to the higher end VIPC618 (which uses shielded high-density D-type connectors to reduce EMI), VIPC616 uses right angle unshielded ribbon cable connectors, which are more cost-effective and suitable for environments that are insensitive to electromagnetic interference or require rapid prototyping. The two software are fully compatible and can be used interchangeably.

Overall characteristics of the board

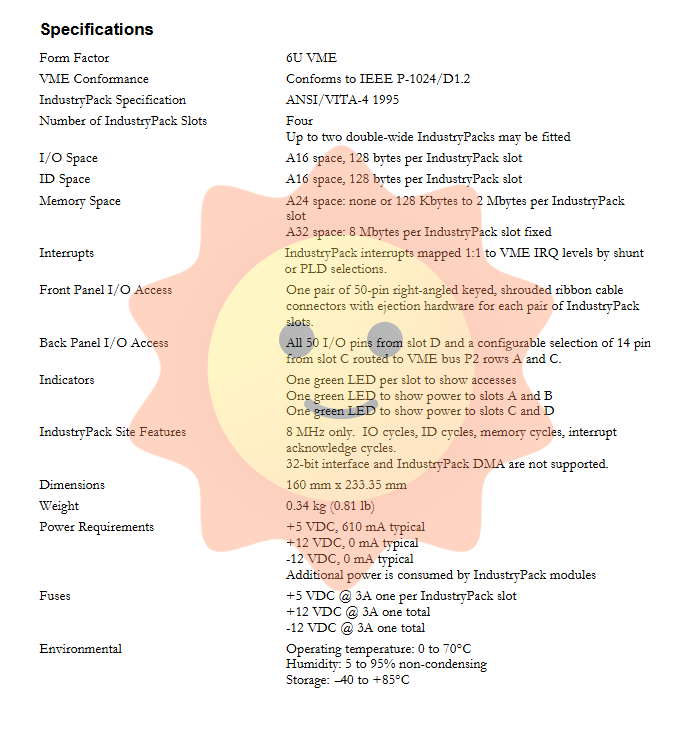

6U VME appearance, compliant with IEEE P-1024/D1.2 and ANSI/VITA-4-1995

Four Industry Pack slots (can accommodate up to two dual wide IPs)

Supports I/O, ID, memory, and interrupt response cycles

Front end I/O uses a pair of 50 pin right angled keyway ribbon cable connectors (with pop-up device) shared by every two IP slots

64 rear I/O are led out through P2 connector (all 50 I/O in D slot+14 I/O optional in C slot)

Memory mapping supports A24 (0-2MB per slot) or A32 (8MB per slot)

128 byte I/O space and 128 byte ID space per IP slot

Green access indicator lights for each slot on the front panel, as well as two sets of power status indicator lights (A/B slot and C/D slot)

All IP power cords are equipped with fuses, RF filters, and decoupling capacitors

Standard interrupt mapping: Jumper blocks map 8 IP interrupt lines one-to-one to VME IRQ1-7

Optional user PLD implementation for arbitrary complex interrupt mapping

Does not support 32-bit IP interface, does not support IP DMA

The IP clock is only 8 MHz

Detailed explanation of address space and memory mapping

VIPC616 maps the three address spaces of IndustriePack to VMEbus:

1. I/O space

VME bus access: A16/D16, fixed 128 bytes per IP slot

Support user mode and super user mode

Supports test and set operations, suitable for semaphores in multi master device systems

2. ID space

Also 128 bytes, read-only, used to identify the manufacturer, model, and version of the IP module

3. Memory space

Optional mapping to A24 or A32

If A24 is selected: Each slot can be configured as no memory, 128KB, 256KB, 512KB, 1MB, or 2MB (set through jumper or PLD)

If A32 is chosen: Each slot supports 8MB of fixed memory, fully utilizing the upper limit of IP specifications

Note: A24 and A32 cannot be used in different slots at the same time. The entire carrier board uses the same memory mapping mode

This flexibility allows VIPC616 to work with both low-end IP modules (requiring only a small memory window) and accommodate data acquisition or image processing IPs that require large buffers.

Deep analysis of interrupt architecture

The interrupt handling of VIPC616 is one of the key factors in its practicality.

Each IndustriePack can generate up to two interrupt requests (such as INT0 and INT1), with a total of 8 interrupt requests across four IPs.

Default configuration: Map 8 interrupt lines one-to-one to 7 interrupt levels (IRQ1-IRQ7) of VMEbus through a set of jumpers. Due to 8>7, one line will be mapped to a reserved or unused level, usually designed for reasonable allocation.

Advanced configuration: Users can program PLDs (Programmable Logic Devices) to plug into onboard sockets, enabling arbitrary interrupt mapping logic, such as:

Multiple IP interrupts share the same VME IRQ

Interrupt priority encoding (encoding 8 lines into 3 lines)

Level/Edge Conversion

Interrupt blocking and routing

The original factory can provide pre programmed PLD versions, please contact the factory for customization.

For most applications, default jumper mapping is sufficient. However, in complex multi interrupt systems, custom PLDs can greatly simplify the design of software interrupt service programs.

I/O signal routing strategy: dual path for front and rear panels

The unique advantage of VIPC616 is that I/O signals can be led out from both the front panel and the backplane P2, and even used simultaneously (note the load).

front panel

Every two IP slots (such as A+B, C+D) share a pair of 50 pin ribbon cable connectors.

The connector is right angled, with keyway and pop-up device for easy insertion and extraction.

The signal is directly connected to the I/O pin of the corresponding IP module.

Backboard P2

All 50 I/O pins of slot D are routed to rows A and C of the P2 connector.

There are 14 configurable I/O pins in slot C that can be routed to P2 (which 14 pins can be selected through jumper or PLD).

The I/O of slots A and B is not routed to P2 and is only available on the front panel.

This design allows system integrators to extract some or all of the IP I/O signals from the back of the chassis, simplifying front cable management, especially suitable for rack mounted VME systems. For example, high-density analog input IP I/O can be connected from P2 to the rear terminal block, while leaving the front panel for debugging or temporary connections.

Power protection and monitoring circuit

VIPC616 has made careful consideration in terms of power integrity:

Each IP slot has independent fuses for+5V,+12V, and -12V. When an IP module experiences overcurrent or short circuit, only the fuse in that slot is blown, without affecting other slots and the VME backplane.

RF filtering and decoupling capacitors: suppress power noise from the backplane and provide clean power for the IP module.

Two power detection circuits:

Monitor the power status of slot A and slot B

Another monitor is the power status of slots C and D

Front panel green LED:

One access LED per slot: When the VME master device accesses the I/O, ID, or memory space of that IP, the LED flashes.

Two power LEDs: indicating that the A/B slot power supply is normal and the C/D slot power supply is normal, respectively. If the LED goes out, the corresponding fuse may have blown or there may be a circuit fault.

These diagnostic functions are extremely practical in on-site maintenance and debugging, and can quickly locate faulty IP or power issues.

Clock and unsupported function limitations

VIPC616 only provides an 8 MHz IP clock. Although the Industry Pack specification allows for 8 MHz or 32 MHz, many modern IP modules may require 32 MHz to achieve full speed. Therefore, when selecting an IP module, it is necessary to confirm its support for an 8 MHz clock.

In addition, the following features are explicitly not supported:

32-bit IP interface (IP module can only operate in 8-bit or 16 bit mode)

IndustriePack DMA (meaning that the IP module cannot initiate VME bus data transfer actively and can only be accessed by the VME master device through Programmed I/O)

These limitations mean that VIPC616 is not suitable for applications that require high data throughput or DMA offloading, such as high-speed video capture or real-time data recording. For such requirements, VIPC618 or higher-level carrier boards should be considered.

Physical dimensions, weight, and environmental specifications

Board size: 160 mm × 233.35 mm (standard 6U)

Weight: 0.34 kg (0.81 lb)

Self power consumption (without IP module):

+5 V: 610 mA (typical)

+12 V:0 mA

-12 V:0 mA

Maximum power supply that can be provided for IP modules:

+5 V: 3 A per slot (12 A in total for four slots, but limited by backplane power supply capacity)

+12 V: Total 3 A (shared by all slots)

-12 V: Total 3 A (shared by all slots)

Working temperature: 0 ° C to+70 ° C (commercial/industrial grade)

Storage temperature: -40 ° C to+85 ° C

Humidity: 5% to 95%, non condensing

For applications that require an extended temperature range (-40 ° C to+85 ° C operation) or high vibration resistance, it is recommended to use the VIPC664-WL (wedge lock) or VIPC664WL-CC (conduction cooling) versions.

Engineering kit (EK-VIPC616)

For the convenience of system integration and secondary development, VIPC616 provides a complete engineering kit, including:

Printed hardware user manual (detailed instructions on jumper settings, connector pin definitions, memory configuration, etc.)

Bill of Materials (BOM)

Circuit schematic (for fault analysis and customized modifications)

Assembly drawing (guiding mechanical assembly)

These materials are very valuable for maintenance, reverse engineering, or developing custom interrupt PLDs.

Related product matrix

Product Model Description

VIPC618 is the same as VIPC616, but the front panel I/O uses shielded high-density 50 pin D-type connectors with locking for better EMI performance

VIPC664-ET rear I/O version (via P2 only), front panel without connector, suitable for full rear wiring

VIPC664-WL VIPC664 with wedge-shaped locking device, anti vibration reinforcement

VIPC664WL-CC conduction cooling version, suitable for fanless, wide temperature, high reliability military systems

VIPC860-FP 6U VME single board computer, integrated with MPC860T processor, with four IP slots, I/O leads from the front panel

VIPC860-BP is the same as above, but I/O is led out from backplane P2

C-IP50F-IP50F-3/6 3-foot or 6-foot long, 50 core ribbon cable, used to connect the front panel to the terminal board or equipment

IP-TERM 50 screw terminal block with ribbon cable connector for easy on-site wiring

These associated products enable systems based on VIPC616 to be flexibly upgraded, expanded, or replaced without the need for significant software modifications.

Typical application cases

Old radar test bench: using VIPC616 in conjunction with ARINC-429, RS-422, and discrete I/O IP modules to simulate aviation bus signals, replacing the discontinued dedicated interface board.

Medical ultrasound front-end: Install a four channel high-speed A/D IP module on VIPC616, implement large capacity data caching through A32 memory mapping, and perform real-time beamforming on a VME single board computer.

Industrial robot controller: using digital I/O IP, encoder IP, and analog output IP, connected to the VME CPU board through VIPC616, to achieve six axis motion control.

Telecommunications Protocol Converter: Multiple synchronous serial IP modules are connected to the VME CPU through VIPC616 for HDLC frame processing.

Integration precautions and common problems

Dual width IP occupancy: If using a dual width IP, it must be placed in slot A+B or C+D, and the corresponding front panel ribbon connector is still available, but other IPs cannot be installed in the other slot.

P2 routing configuration: What are the 14 optional I/O pins for slot C? Please refer to the jumper configuration table in the user manual for details. The default may be the lower 14 pins.

Interrupt sharing issue: Under the default one-to-one mapping, if two IPs use the same VME IRQ level, software support for chain interrupts or polling is required. Custom PLD can solve this problem.

8 MHz clock compatibility: If the IP module requires 32 MHz, you can consider modifying the carrier board clock (not recommended) or using a carrier board that supports 32 MHz (such as some third-party designs).

Replacement for DMA deficiency: For IPs that require high throughput, IPs with local FIFO or dual port RAM can be selected and read by the VME master device through block transfer (BLT).

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba