TI 11kW GaN three-phase ANPC inverter

TI 11kW GaN three-phase ANPC inverter: ushering in a new era of high power density energy conversion

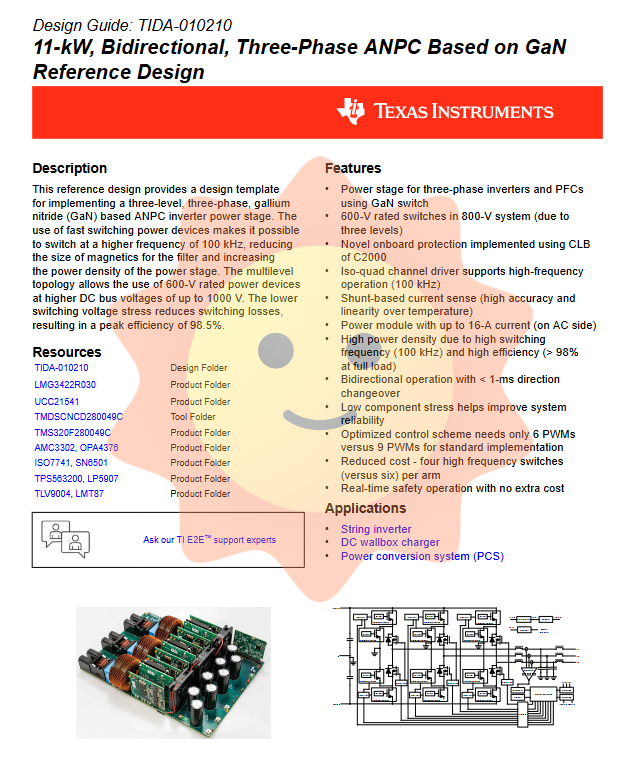

In modern renewable energy systems, especially solar inverters and energy storage systems, the demand for higher efficiency, higher power density, and bidirectional energy flow capability is increasing. To address these challenges, a reference design based on gallium nitride (GaN) active midpoint clamping (ANPC) topology has emerged. This design provides an 11kW, bidirectional, three-phase inverter power level template, achieving significant performance leaps through innovative topology and advanced wide bandgap semiconductor devices.

Technical background and design challenges

Commercial and utility grade solar inverters are undergoing various technological innovations. The market clearly points towards three main directions: firstly, increasing the voltage of solar arrays to 1000V or even 1500V DC to reduce the current at the same power level, thereby reducing conduction losses and improving efficiency; Secondly, efforts should be made to reduce the size of onboard magnetic components in order to increase power density; Finally, in order to meet the local energy storage needs, the inverter must have bidirectional power transmission capability.

However, the evolution towards higher DC bus voltages has encountered bottlenecks. In the traditional half bridge topology, each switching device must withstand the complete input voltage, which greatly limits the selection of low-cost, high-speed power devices. To overcome this obstacle, multi-level topology has become an ideal solution. This reference design demonstrates a three-level ANPC converter that cleverly limits the voltage stress of all power devices to half of the DC bus voltage, allowing for the use of better performing and more abundant 600V rated voltage devices.

ANPC topology architecture and working principle

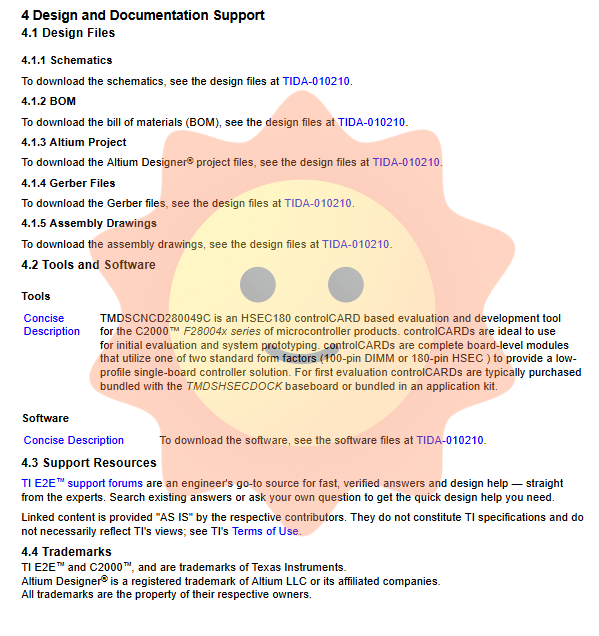

The core of this reference design is its three-phase ANPC power stage. Unlike traditional two-level topologies, ANPC topology contains six switches per phase. Although this complex structure increases the difficulty of driving and protection, it lays the foundation for achieving high efficiency and high-voltage operation.

Simplified control strategy: The design adopts a relatively simplified control scheme, using the upper half (Q1, Q5, Q2) and lower half (Q4, Q6, Q3) of each phase for positive and negative half cycle operation, respectively. Q2 and Q3 serve as low-frequency switches (50/60Hz), responsible for connecting inductors to the upper GaN high-frequency switch pair (Q1 and Q5) or the lower GaN high-frequency switch pair (Q4 and Q6). Each high-frequency switch operates in synchronous buck converter mode during its corresponding half cycle.

Detailed explanation of working mode:

Positive half cycle: Q2 remains conductive. When Q1 is conducting, the circuit is in active mode, and the inductor is connected to the positive bus (V+) to establish current. At the same time, to ensure balanced voltage stress on Q3 and Q4 (which need to jointly withstand the full bus voltage), Q6 is also turned on, connecting the center node to the neutral point to evenly distribute the voltage. During the dead time, the inductor current passes through the body diode of Q5 and the continuous current of Q2, which remains conductive. At this time, Q5 acts as a synchronous rectifier and connects the inductor switch node to the neutral point.

Negative half cycle: The working principle is symmetrical with the positive half cycle, and Q3 is fully conductive. In active mode, Q4 conducts, the inductor is connected to the negative bus (V -), and Q5 conducts to balance the voltage stress of Q1 and Q2. In freewheeling mode, the current is maintained through Q6 and Q3, connecting the inductor node to the neutral point.

Core design features and advantages

This reference design is not only a topology concept, but also a validated and complete hardware and software solution with multiple outstanding features.

1. Innovative applications of GaN devices

The design adopts TI's LMG3422R030 GaN FET (600V, 30m Ω). GaN devices, with their extremely low switching losses and lack of reverse charge recovery, make it possible to significantly increase the switching frequency. In this design, the operating frequency of high-frequency switches (Q1, Q4, Q5, Q6) is as high as 100kHz, much higher than traditional silicon-based designs (typically 16-32kHz). High frequency directly reduces the volume of inductors in the output filter (LCL), which is the key to improving power density. Meanwhile, Q2 and Q3 still use low-cost 650V Si MOSFETs, achieving a balance between performance and cost.

2. High DC bus voltage capability

Through a three-level ANPC topology, a single 600V GaN device is safely applied in an 800V DC bus system. This directly responds to the trend of photovoltaic systems developing towards high voltage, reducing current levels and conduction losses. Designed to support a wide input voltage range of 600V to 800V.

3. Protection mechanism for innovation

One major challenge of multi-level topology is to avoid device overvoltage in abnormal situations. This design utilizes the configurable logic block (CLB) in the C2000 microcontroller series to achieve novel onboard hardware protection, enabling interlocking protection between devices under all operating conditions without the need for additional components, preventing overvoltage, and improving system reliability.

4. Optimized control and driving

By optimizing the control scheme, the entire power stage (consisting of 18 power devices) can be driven with only 6 PWM signals, while the traditional scheme requires 9, greatly saving MCU resources. At the same time, ISO7741 isolators are used to achieve PWM signal isolation, and the fault signals of GaN devices can be transmitted back to the MCU in reverse, achieving real-time safe operation.

5. Bi directional operation capability

The ANPC power stage itself has the inherent ability for bidirectional energy flow. Through software configuration, it can act as an inverter (DC-AC) to feed solar or battery energy into the grid, or as a power factor corrector (PFC, AC-DC) to store grid energy in local batteries. The document states that the inverter mode has passed the test, PFC mode testing is currently underway, and the direction switching time is less than 1 millisecond.

Key system design and component selection

Design of LCL Filter

To achieve high-quality grid connected current and effectively attenuate high-frequency harmonics, LCL filters were designed and adopted. At a switching frequency of 100kHz, the inductance (L_inv) value on the inverter side can be significantly reduced. The calculated value of L_inv is approximately 360 μ H (considering the influence of bias current). The filtering capacitor (Cf) is selected to be 4.7 μ F to limit the absorbed reactive power to below 3.5% of the total power. To obtain a 5% attenuation factor, the grid side inductance (L_grid) was calculated to be approximately 10.3 μ H, and a standard value of 15 μ H was ultimately selected. The calculated resonant frequency (approximately 19.35kHz) meets the stability requirements of being much higher than the power frequency and lower than half of the switching frequency. In addition, a 0.58 Ω damping resistor is connected in series to suppress resonance peaks.

Current and voltage detection

Current detection: AMC3302 enhanced isolated current sensor is used, which integrates an isolated bias power supply, greatly simplifying the design. The sensor has a small input range of ± 50mV, coupled with a high-precision shunt resistor of 2m Ω, producing only 0.5W loss at full power (about ± 25A), achieving a perfect balance between high precision and low loss.

Voltage detection: Voltage sampling is performed at three points before and after the output relay, as well as on the positive and negative busbars. Attenuate high voltage signals through a resistive voltage divider network and add a bias voltage of 1.65V to match the input range of the ADC. This design allows the control system to lock the grid voltage and frequency before grid connection, and independently adjust the duty cycle of the positive and negative half cycles to balance the bus voltage.

Power supply and driver

Auxiliary power supply: The system is powered by a 12V main bias power supply. The TPS563200 buck converter generates 5V, and then LP5907 LDO generates 3.3V for use in analog and logic circuits. For each GaN or Si device on the power card, an SN6501 transformer driver is used in conjunction with different transformers to generate isolated 12V (GaN) or+12V/-5V (Si MOSFET) driving voltages.

Si MOSFET driver: For low-frequency Si power boards, a dual channel isolated driver UCC21541 is used, which can simultaneously drive two devices on one power board. The independent conduction and turn off paths, as well as the ferrite beads in the gate path, effectively control the driving current and suppress ringing.

Test validation and performance evaluation

The reference design has been strictly tested to verify its progressiveness in theory and reliability in practice.

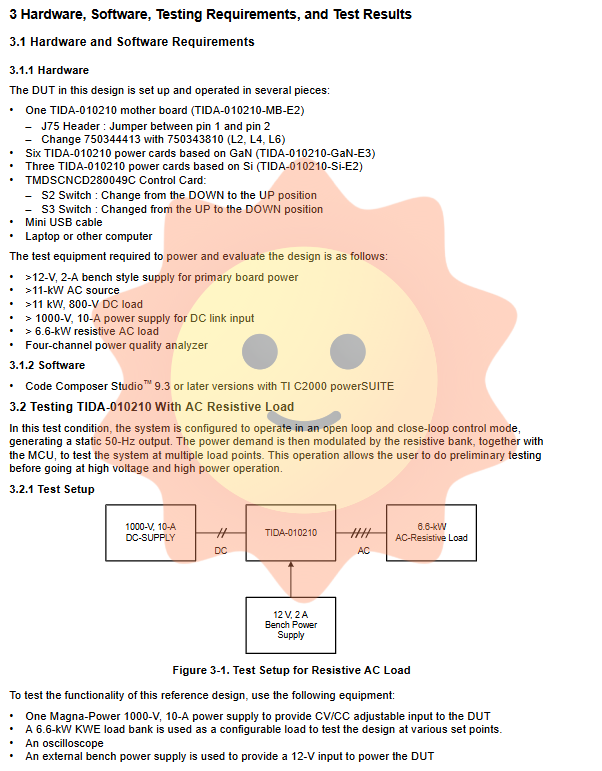

Inverter mode test (resistive load)

Under open-loop and closed-loop control, the system generated a pure 50Hz sine waveform at an 800V DC bus voltage. The test results show that even near zero crossing, waveform distortion is minimal, thanks to the protection mechanism based on CLB. The stability of the current loop has been verified through the step response of the current from 1A to 6A and the reverse direction, demonstrating smooth transient transition capability.

PFC mode testing and efficiency

In PFC mode, the system operated at a grid voltage of 230Vrms and tested its efficiency at 600V and 800V DC bus voltages, respectively. The test results are remarkable:

High efficiency: Within the load range of 2kW to 11kW, the system efficiency remains above 98%, with a peak efficiency of 98.62%.

Voltage selection strategy: Data shows that using a lower 600V bus voltage is more efficient at low power, while maintaining an 800V bus voltage can bring about a 0.4% efficiency improvement at high power (high current).

Low harmonic: Under rated load, the current waveform has good sinuosity and total harmonic distortion (THD) is less than 4%.

power density

The final physical dimensions of the design are 300mm (length) x 220mm (width) x 65mm (height), with a total volume of only 4.29 liters. At a rated power of 11 kW, the achieved power density is as high as 2.57 kW/L, which fully demonstrates the huge advantage of high-frequency GaN switches in reducing the volume of passive components.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba