TI 11kW GaN three-phase ANPC inverter

TI 11kW GaN three-phase ANPC inverter: ushering in a new era of high power density energy conversion

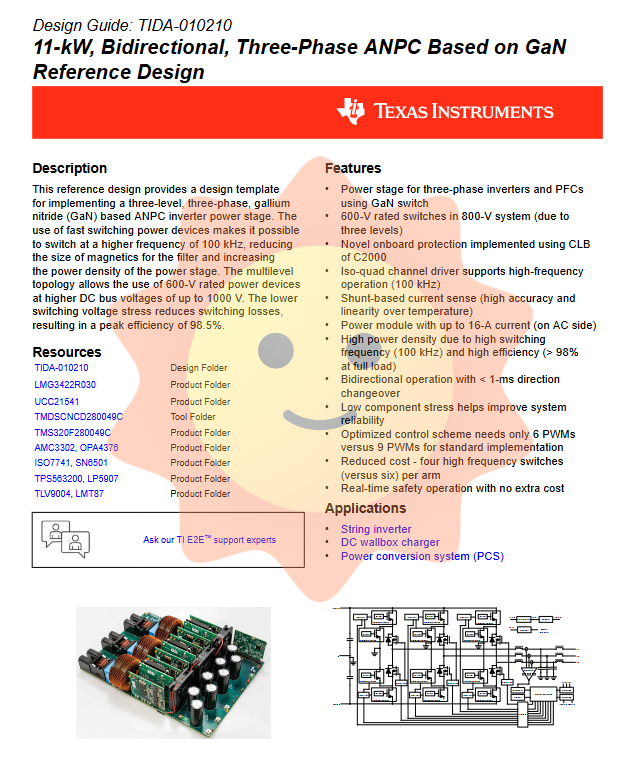

In modern renewable energy systems, especially solar inverters and energy storage systems, the demand for higher efficiency, higher power density, and bidirectional energy flow capability is increasing. To address these challenges, a reference design based on gallium nitride (GaN) active midpoint clamping (ANPC) topology has emerged. This design provides an 11kW, bidirectional, three-phase inverter power level template, achieving significant performance leaps through innovative topology and advanced wide bandgap semiconductor devices.

Technical background and design challenges

Commercial and utility grade solar inverters are undergoing various technological innovations. The market clearly points towards three main directions: firstly, increasing the voltage of solar arrays to 1000V or even 1500V DC to reduce the current at the same power level, thereby reducing conduction losses and improving efficiency; Secondly, efforts should be made to reduce the size of onboard magnetic components in order to increase power density; Finally, in order to meet the local energy storage needs, the inverter must have bidirectional power transmission capability.

However, the evolution towards higher DC bus voltages has encountered bottlenecks. In the traditional half bridge topology, each switching device must withstand the complete input voltage, which greatly limits the selection of low-cost, high-speed power devices. To overcome this obstacle, multi-level topology has become an ideal solution. This reference design demonstrates a three-level ANPC converter that cleverly limits the voltage stress of all power devices to half of the DC bus voltage, allowing for the use of better performing and more abundant 600V rated voltage devices.

ANPC topology architecture and working principle

The core of this reference design is its three-phase ANPC power stage. Unlike traditional two-level topologies, ANPC topology contains six switches per phase. Although this complex structure increases the difficulty of driving and protection, it lays the foundation for achieving high efficiency and high-voltage operation.

Simplified control strategy: The design adopts a relatively simplified control scheme, using the upper half (Q1, Q5, Q2) and lower half (Q4, Q6, Q3) of each phase for positive and negative half cycle operation, respectively. Q2 and Q3 serve as low-frequency switches (50/60Hz), responsible for connecting inductors to the upper GaN high-frequency switch pair (Q1 and Q5) or the lower GaN high-frequency switch pair (Q4 and Q6). Each high-frequency switch operates in synchronous buck converter mode during its corresponding half cycle.

Detailed explanation of working mode:

Positive half cycle: Q2 remains conductive. When Q1 is conducting, the circuit is in active mode, and the inductor is connected to the positive bus (V+) to establish current. At the same time, to ensure balanced voltage stress on Q3 and Q4 (which need to jointly withstand the full bus voltage), Q6 is also turned on, connecting the center node to the neutral point to evenly distribute the voltage. During the dead time, the inductor current passes through the body diode of Q5 and the continuous current of Q2, which remains conductive. At this time, Q5 acts as a synchronous rectifier and connects the inductor switch node to the neutral point.

Negative half cycle: The working principle is symmetrical with the positive half cycle, and Q3 is fully conductive. In active mode, Q4 conducts, the inductor is connected to the negative bus (V -), and Q5 conducts to balance the voltage stress of Q1 and Q2. In freewheeling mode, the current is maintained through Q6 and Q3, connecting the inductor node to the neutral point.

Core design features and advantages

This reference design is not only a topology concept, but also a validated and complete hardware and software solution with multiple outstanding features.

1. Innovative applications of GaN devices

The design adopts TI's LMG3422R030 GaN FET (600V, 30m Ω). GaN devices, with their extremely low switching losses and lack of reverse charge recovery, make it possible to significantly increase the switching frequency. In this design, the operating frequency of high-frequency switches (Q1, Q4, Q5, Q6) is as high as 100kHz, much higher than traditional silicon-based designs (typically 16-32kHz). High frequency directly reduces the volume of inductors in the output filter (LCL), which is the key to improving power density. Meanwhile, Q2 and Q3 still use low-cost 650V Si MOSFETs, achieving a balance between performance and cost.

2. High DC bus voltage capability

Through a three-level ANPC topology, a single 600V GaN device is safely applied in an 800V DC bus system. This directly responds to the trend of photovoltaic systems developing towards high voltage, reducing current levels and conduction losses. Designed to support a wide input voltage range of 600V to 800V.

3. Protection mechanism for innovation

One major challenge of multi-level topology is to avoid device overvoltage in abnormal situations. This design utilizes the configurable logic block (CLB) in the C2000 microcontroller series to achieve novel onboard hardware protection, enabling interlocking protection between devices under all operating conditions without the need for additional components, preventing overvoltage, and improving system reliability.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba