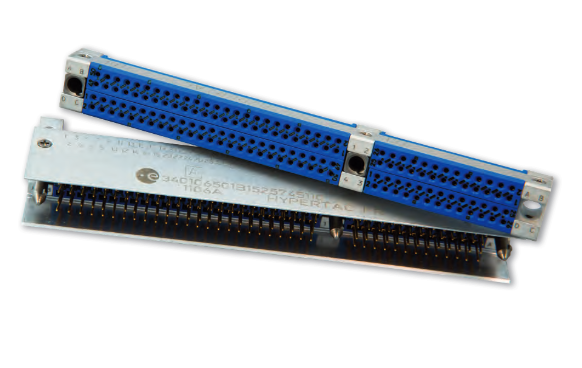

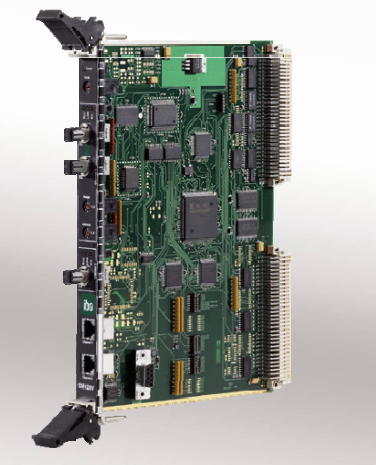

GE VMIVME-5588 High-Speed Reflective Memory

GE VMIVME-5588 High-Speed Reflective Memory

DESCRIPTION

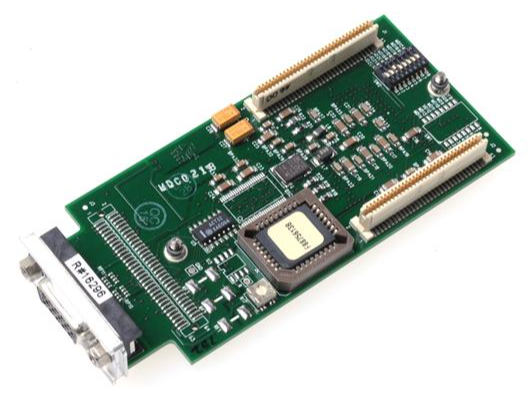

VMIVME-5588 is a high-performance, daisy-chained VME-to-VME network. Data is transferred by writing to on-board global RAM. The data is automatically sent to the location in memory on all Reflective Memory boards on the network.The Reflective Memory concept provides a very fast and efficient way of sharing data across distributed computer systems.

VMIC’s VMIVME-5588 Reflective Memory interface allows data to be shared between up to 256 independent systems (nodes) at rates up to 29.5 Mbyte/s. Each Reflective Memory board may be configured with 256 Kbyte to 16 Mbyte of on-board SRAM. The local SRAM provides fast Read access times to stored data. Writes are stored in local SRAM and broadcast over a high-speed data path to other Reflective Memory nodes. The transfer of data between nodes is software transparent, so no I/O overhead is required. Transmit and Receive FIFOs buffer data during peak data rates to optimize CPU and bus performance to maintain high data throughput.

FEATURES

• High-speed, easy-to-use network (1.2 Gbaud serially)

• Data written to memory in one node is also written to memory in all nodes on the network

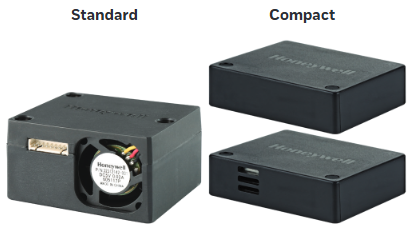

• Up to 1,000 ft between nodes with multimode fiber, 10 km with single mode, 30 m with twinax

• Supports up to 256 nodes

• Data transferred at 29.5 Mbyte/s without redundant transfer

• Data transferred at 14.8 Mbyte/s with redundant transfer

• Any node on the network can generate an interrupt in any other node on the network or in all network nodes with a single command

• Error detection • Redundant transmission mode for suppressing errors

• No processor overhead

• No processor involvement in the operation of the network

• Up to 16 Mbyte of Reflective Memory

• A24:A32:D32:D16:D8 memory access

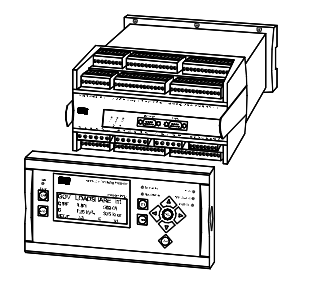

• Two-slot 6U VMEbus board

• Any node may reset any or all other nodes

• Software compatible with VMIVME-5578

• Software-addressable digital output bit (available at front panel and P2 connector) for interfacing with the VMIVME-5599 optical switch board or any user-defined purpose • Multimode or single-mode fiber-optic or twinax cable options

LINK ARBITRATION

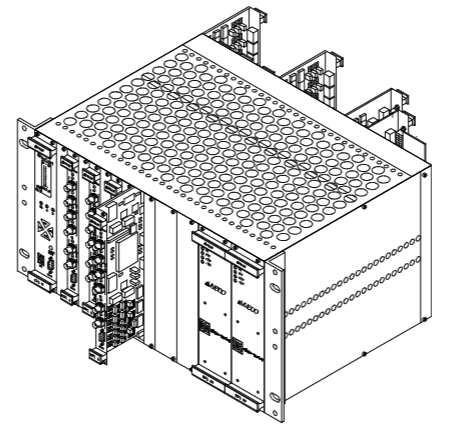

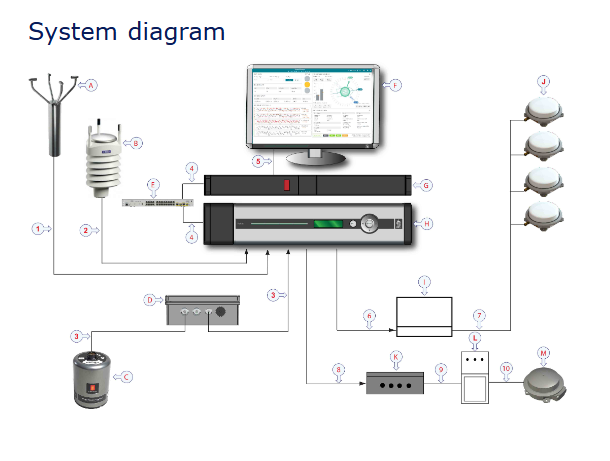

The VMIVME-5588 system is a daisy-chain ring as shown in Figure 1. Each transfer is passed from node-to-node until it has gone all the way around the ring and reaches the originating node. Each node retransmits all transfers that it receives except those that it originated. Nodes are allowed to insert transfers between transfers passing through.

INTERRUPT TRANSFERS

In addition to transferring data between nodes, the VMIVME-5588 will allow any processor in any node to generate an interrupt on any other node. These interrupts would generally be used to indicate to the receiving node that new data has been sent and is ready for processing. These interrupts are also used to indicate that processing of old data is completed and the receiving node is ready for new data.

ERROR MANAGEMENT

Errors are detected by the VMIVME-5588 with the use of the error detection facilities of the Fiber Channel encoder/decoder and additional interlaced parity encoding and checking. The error rate of the VMIVME-5588 is a function of the rate of errors produced in the cable portion of the system. This optical error rate depends on the length and type of fiber-optic cable. Assuming an optical error rate of 10-12, the error rate of the VMIVME-5588 is 1.3 x 10-10 transfers/transfer.

However, the rate of undetectable errors is less than 1.64 x 10-20 transfers/transfer. When a node detects an error, the erroneous transfer is removed from the system and a VMEbus interrupt is generated, if enabled.

The VMIVME-5588 can be operated in a redundant transfer mode in which each transfer is transmitted twice. In this mode of operation, the first of the two transfers is used unless an error is detected in which case the second transfer is used. In the event that an error is detected in both transfers, the node removes the transfer from the system. The probability of both transfers containing an error is 1.64 x 10-20, or about one error every 317,855 years at maximum data rate.

PROTECTION AGAINST LOST DATA

Data received by the node from the fiber-optic cable is error checked and placed in a receive FIFO. Arbitration with accesses from the VMEbus then takes place and the data is written to the node’s SRAM and to the node’s transmit FIFO. Data written to the board from the VMEbus is placed directly into SRAM and into the transmit FIFO. Data in the transmit FIFO is transmitted by the node over the cable to the next node. Data could be lost if either FIFO were allowed to become full.

The product is designed to prevent either FIFO from becoming full and overflowing. It is important to note the only way that data can start to accumulate in FIFOs is for data to enter the node at a rate greater than 29.5 Mbyte/s or 14.8 Mbyte/s in redundant mode. Since data can enter from the fiber and from the VMEbus, it is possible to exceed these rates. If the transmit FIFO becomes half-full, a bit in the Status Register is set and, if enabled, an interrupt is generated. This is an indication to the node’s software that subsequent WRITEs to the Reflective Memory should be suspended until the FIFO is less than half-full. If the half-full indication is ignored and the transmit FIFO becomes full, then writes to the Reflective Memory will not be acknowledged until access is granted or the CPU times out with a Bus Error.

- User name Member Level Quantity Specification Purchase Date

- Satisfaction :

-