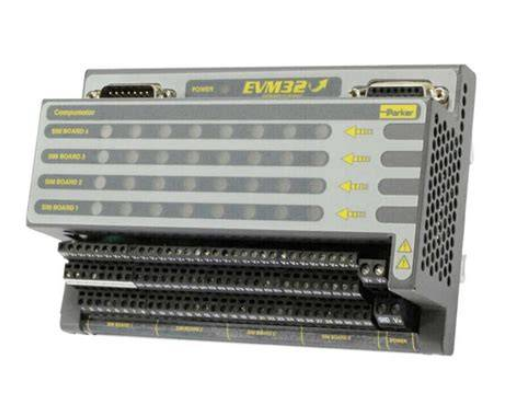

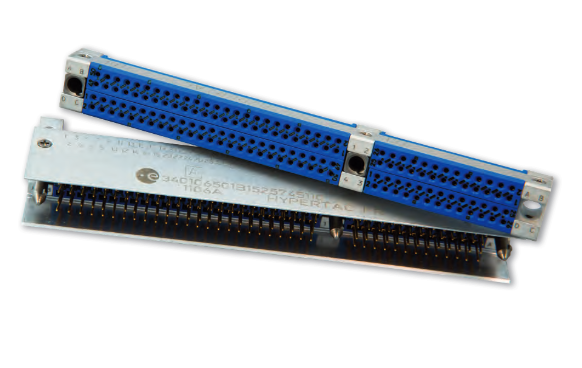

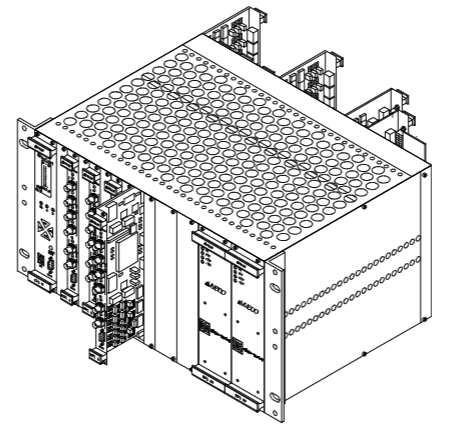

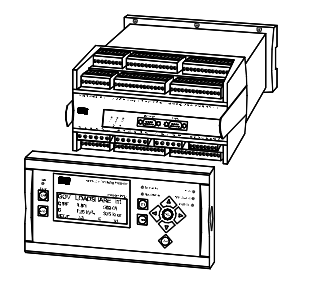

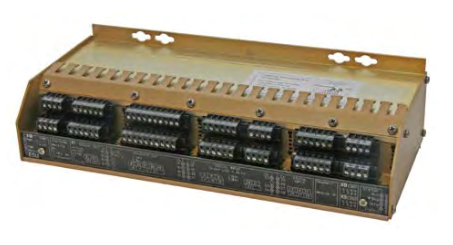

GE IS200DPWAG1A-1 Transducer Power Distribution Terminal Board

GE IS200DPWAG1A-1 Transducer Power Distribution Terminal Board

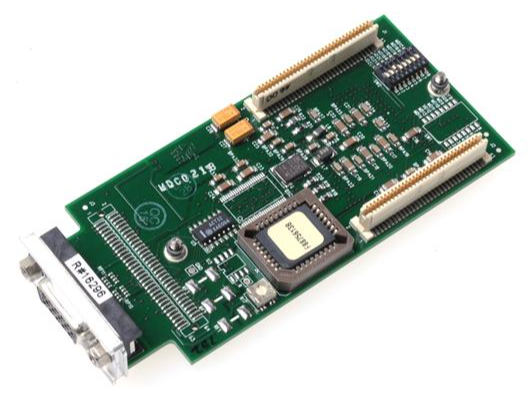

Part Number IS200DPWAG1A-1 Manufacturer General Electric Country of Manufacture As Per GE Manufacturing Policy Series Mark VI/VIe Function Module Availability In StockIS200DSPXH1C functions as Digital Signal Processor Control Board developed by GE. It is the primary controller for the bridge, motor regulator, and gating functions in Innovation Series drives. Specialized Hardware Functions Custom logic in Field Programmable Gate Arrays (FPGA) or ASICs with supporting circuits is used to provide specialized functions on the DSPX board. ASICs contain the majority of specialized and support functions.

P1 has four serial interfaces, which are as follows: Two 5 Mb/s ISBusTM interfaces that can be used as master or slave One asynchronous TTL interface for a computer-based configuration tool, with RX, TX, and TXEN/RTS data signals One asynchronous TTL interface to a programmer board, including data signals RX, TX, and RTS Synchronizing load pulse signals accomplishes the following tasks: An inner loop load pulse signal records I/O values such as bridge, motor, or generator voltages and currents, as well as VCOs, tachometer counters, and discrete inputs. It can also synchronize ISBus channels, software, and bridge gating outputs. An application loop load pulse signal is used to capture values of other application VCOs and optionally the tachs at a sub-multiple or multiple of the inner loop load pulse. Onboard Firmware Flash memory stores onboard firmware.

There are three major kinds: The boot loader is in charge of the power-on sequence and should not be reloaded in the field. The specific control functions for the drive or exciter product are defined by application code. This code is loaded via the exciter's Tool port, and configuration parameters are loaded via the toolbox. The Unit Data Highway is used to load exciter parameters. If applicable, drive parameters are loaded to ACL_ via serial port, ISBus, or Ethernet. Indicating Lights DS1: Fault LED driven by the DSP, ON or flashing: A fault has occurred or during reset, OFF: No faults are present DS2: Status monitor LED driven by the DSP, Flashing: Running, ON: Stopped, OFF: A fault has occurred or during reset I/O Definitions The DSPX includes three I/O connectors as follows: P1 backplane connector P5 DSP emulator port P6 engineering monitor port The P1 connector provides memory mapped process bus address space as well as four chip select signals to support bridge and customer input/output (I/O) interfaces.

It also includes controls for a standard UART serial interface to a programmer board and a configuration tool, as well as two additional ISBus proprietary serial interfaces for ACL or local expansion functions. The P5 emulator port (on the board's front panel) connects to the TI emulator port. It includes a scan interface (similar to JTAG) for emulation and FLASH programming. The P6 engineering monitor port (located on the board's front panel) connects to the DSP synchronous serial port and allows only GE engineering users to connect to a terminal. Handling Precautions Static-sensitive components may be found on printed wiring boards. As a result, WOC packages all replacement boards in anti-static bags. When handling boards, follow the following guidelines: Anti-static bags or boxes should be used to store boards. When handling boards or board components, use a grounding strap.

FEATURES:

Stack overflow detection is provided for both the foreground stack (from internal memory) and the background stack (from external SRAM). Interrupt INT0 is generated if either stack overflows. If both stacks overflow, a hard reset is generated. A configuration register is provided to allow the stack overflow reset to be disabled.

A watchdog timer is enabled and periodically toggled by the DSP (toggle interval is configurable). A time-out of the watchdog timer will generate a hard reset. A 24-bit free running timer is also provided and used as a reference for certain functions.

Five differential (HIFI) pair application inputs may be used as two quadrature incremental tach interfaces (one with marker capability). The signals drive two 16-bit up/down counters. It maintains its present state when the inputs are at the same level, and changes state when the inputs are differentially opposite.

A 5 MHz timer resets each time the counter increments or decrements, and a state register records the direction of the last count. Associated with each of these counters, timers, and registers is a capture register that can be configured to capture the values on the occurrence of either the inner loop load pulse or the application loop load pulse.

The five differential HIFI inputs can be used as application layer VCO counters or single-channel tach interfaces. Five 16-bit counters increment on the differentially decoded and filtered inputs. These counter values are captured into registers the DSP can read by the application loop load pulse.

The five differential HIFI inputs can also be used as up to ten discrete inputs. Each input is filtered for three system clock cycles and directly readable by the DSP in a buffer.

Six inputs from the backplane are digitally filtered and input to the VCO counters. These are 16-bit counters with capture registers latched by the inner loop load pulse and readable by the DSP.

- User name Member Level Quantity Specification Purchase Date

- Satisfaction :

-