SIEMIENS S7-1200/1500 Controller TIA Portal Programming Guide

Non optimized blocks;

Array access for runtime calculation index (such as # Array [# i]);

Indirect memory access (such as pointer operations);

Data replication between optimized and non optimized blocks.

Key recommendations:

Replace bit memory with global DB (M-zone): The size of M-zone varies depending on the controller, while global DB is more flexible and supports optimized storage;

Use temporary tag caching for frequently accessed I/O tags to reduce the number of I/O accesses;

Retention setting: Only the necessary labels need to be set to hold (such as process parameters) to reduce the cost of saving power-off data.

3. Addressing method

Symbol addressing (mandatory recommendation):

Advantages: The tag name is descriptive (such as # Motor1_Run) and automatically updates when the address changes, reducing errors;

Operation: Simply enter the symbol name in the instruction input box, right-click on "Define Label" to quickly create it.

Indirect access scheme:

Indirect array access: Replace pointers with # Array [# Index], such as # Temp:=# MotorSpeed [# i];;

Slice access: Directly access the bits/bytes of Byte/Word/DWord, such as # WordVar.% X0 (bits), # DWordVar.% W1 (words).

4. Performance optimization techniques

Disable the ENO evaluation (LAD/FBD) of blocks to reduce runtime detection;

Avoid deep level calling (≤ 8 layers), otherwise TIA Portal will compile alarms and increase protection code overhead;

FOR loop: Do not manipulate the loop counter (compiler optimized times), use EXIT to interrupt the loop;

Reduce unnecessary IF instructions, such as # Motor:=# On1 AND # On2; Replace IF # On1 AND # On2 THEN # Motor:=TRUE; ELSE #Motor:=FALSE; END_IF;。

Hardware independent programming

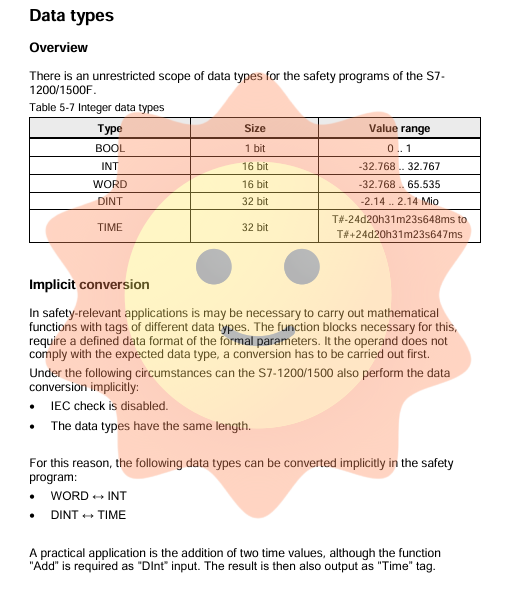

1. Data type compatibility

Only use EN 61131-3 standard data types (such as INT/DINT/REAL/BOOL), avoiding S7-300/400 specific types (such as S5TIME);

The timer/counter of S7-1200/1500 uses IEC standard blocks (such as TON/CUTU) and is integrated through multiple instances to avoid absolute addresses (such as T37).

2. Clock signal replacement

Do not use hardware clock memory (such as M0.5), use programming clock generation block instead:

Example: SCL writes FB, sets the frequency through the # Frequency parameter, # Q outputs pulses, and # Countdown outputs the remaining time;

Advantage: The clock frequency can be flexibly adjusted without relying on hardware configuration.

STEP 7 Safety Programming

1. Core components

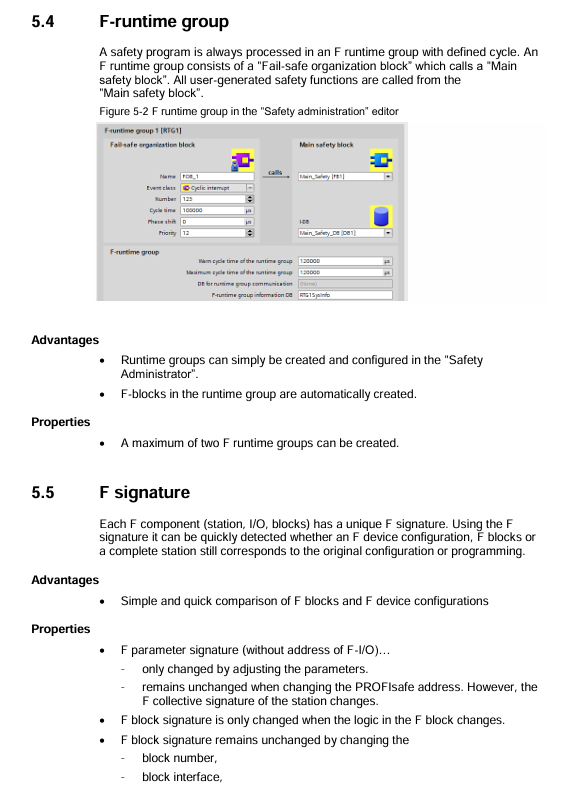

F operation group: the execution unit of safety programs, including 1 fault safety OB and 1 main safety block, with a maximum of 2 created;

F-signature: a unique identifier for each F-component (F-I/O, F-block) used to detect configuration/programming changes;

Security Management Editor: Manage F run groups, F signatures, access permissions, and set security program passwords.

2. Key specifications

Data exchange: Standard programs and security programs only interact through two standard DBs, avoiding direct access to the security DB;

Performance optimization:

Avoid using TP/TON/TOF instructions (add protection code);

Disable the JMP/Label structure (resulting in additional system protection blocks);

Loop call hierarchy ≤ 8 layers;

Test restriction: The security program can only force testing when the security mode is disabled, with a maximum of 5 F-I/O forced at a time.

Visual automatic generation (SiVArc)

1. Basic requirements

Tools: TIA Portal V14++SiVArc Options Package;

Prerequisite: The program is modularized (such as motor control FB, conveyor belt FB), and the visualization library includes standard image templates.

2. Control mode

Network comment: Add a tag (such as "SiVArc: Generate=True") when calling the network on FB. The SiVArc rule triggers generation through Contains (Block. NetworkComment, "Generate=True");

SiVArc variable: Define a variable in the "Plugin" label of the block (such as Location="Bottling_Test"), and the rule filters the generated range based on the variable value.

- ABB

- General Electric

- EMERSON

- Honeywell

- HIMA

- ALSTOM

- Rolls-Royce

- MOTOROLA

- Rockwell

- Siemens

- Woodward

- YOKOGAWA

- FOXBORO

- KOLLMORGEN

- MOOG

- KB

- YAMAHA

- BENDER

- TEKTRONIX

- Westinghouse

- AMAT

- AB

- XYCOM

- Yaskawa

- B&R

- Schneider

- Kongsberg

- NI

- WATLOW

- ProSoft

- SEW

- ADVANCED

- Reliance

- TRICONEX

- METSO

- MAN

- Advantest

- STUDER

- KONGSBERG

- DANAHER MOTION

- Bently

- Galil

- EATON

- MOLEX

- DEIF

- B&W

- ZYGO

- Aerotech

- DANFOSS

- Beijer

- Moxa

- Rexroth

- Johnson

- WAGO

- TOSHIBA

- BMCM

- SMC

- HITACHI

- HIRSCHMANN

- Application field

- XP POWER

- CTI

- TRICON

- STOBER

- Thinklogical

- Horner Automation

- Meggitt

- Fanuc

- Baldor

- SHINKAWA

- Other Brands

- UniOP

- KUKA

- Iba